126

CHAPTER 5 I/O Port

■ Registers for Port 5

●

Port 5 data register (PDR5)

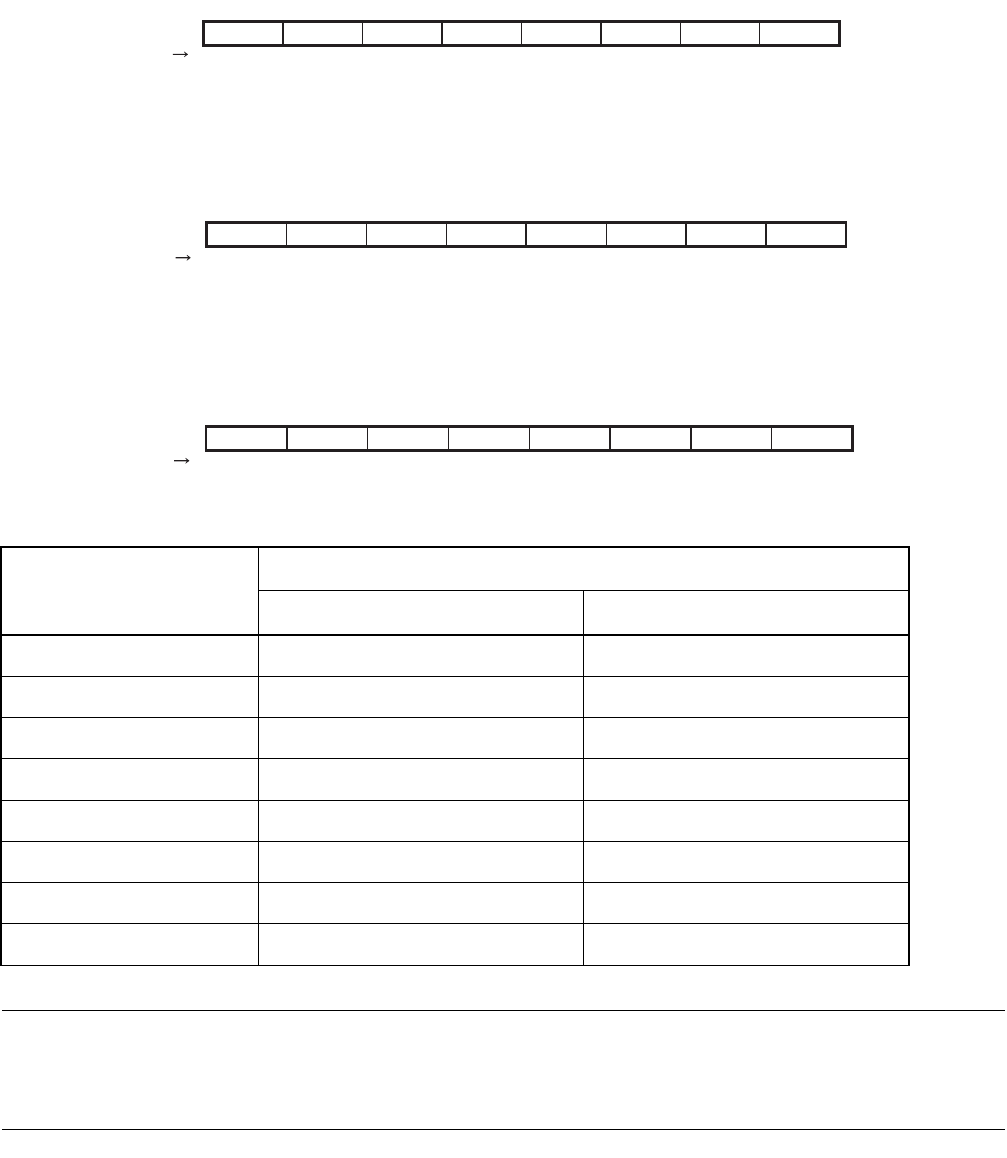

Figure 5.5-2 Port 5 data register (PDR5)

●

Port 5 direction register (DDR5)

Figure 5.5-3 Port 5 direction register (DDR5)

●

Port 5 function selection register (PFS5)

Figure 5.5-4 Port 5 function selection register (PFS5)

Note:

The * setting is only valid when the external bus mode is specified. The general-purpose port

function is always selected for single-chip mode.

Table 5.5-1 Operation of function selection bits

Function selection bit

Register setting value

0 1

[bit7]: A15E General-purpose port

Address (A15) output

*

[bit6]: A14E General-purpose port

Address (A14) output

*

[bit5]: A13E General-purpose port

Address (A13) output

*

[bit4]: A12E General-purpose port

Address (A12) output

*

[bit3]: A11E General-purpose port

Address (A11) output

*

[bit2]: A10E General-purpose port

Address (A10) output

*

[bit1]: A09E General-purpose port

Address (A09) output

*

[bit0]: A08E General-purpose port

Address (A08) output

*

7 6 5 4 3 2 1 0

XXXX XXXX

B

Initial value

bit

R/W R/W R/W R/W R/W R/W R/W R/W

PD57 PD56 PD55 PD54 PD53 PD52 PD51 PD50

Access

Address: 000006

H

7 6 5 4 3 2 1 0

0000 0000

B

Initial value

bit

WWWWWWWW

DR57 DR56 DR55 DR54 DR53 DR52 DR51 DR50

Access

Address: 00000E

H

7 6 5 4 3 2 1 0

1111 1111

B

Initial value

bit

WWWWWWWW

A15E A14E A13E A12E A11E A10E A09E A08E

Access

Address: 000606

H