175

8.5 Operation of PPG

The operation of PPG has output and start operation.

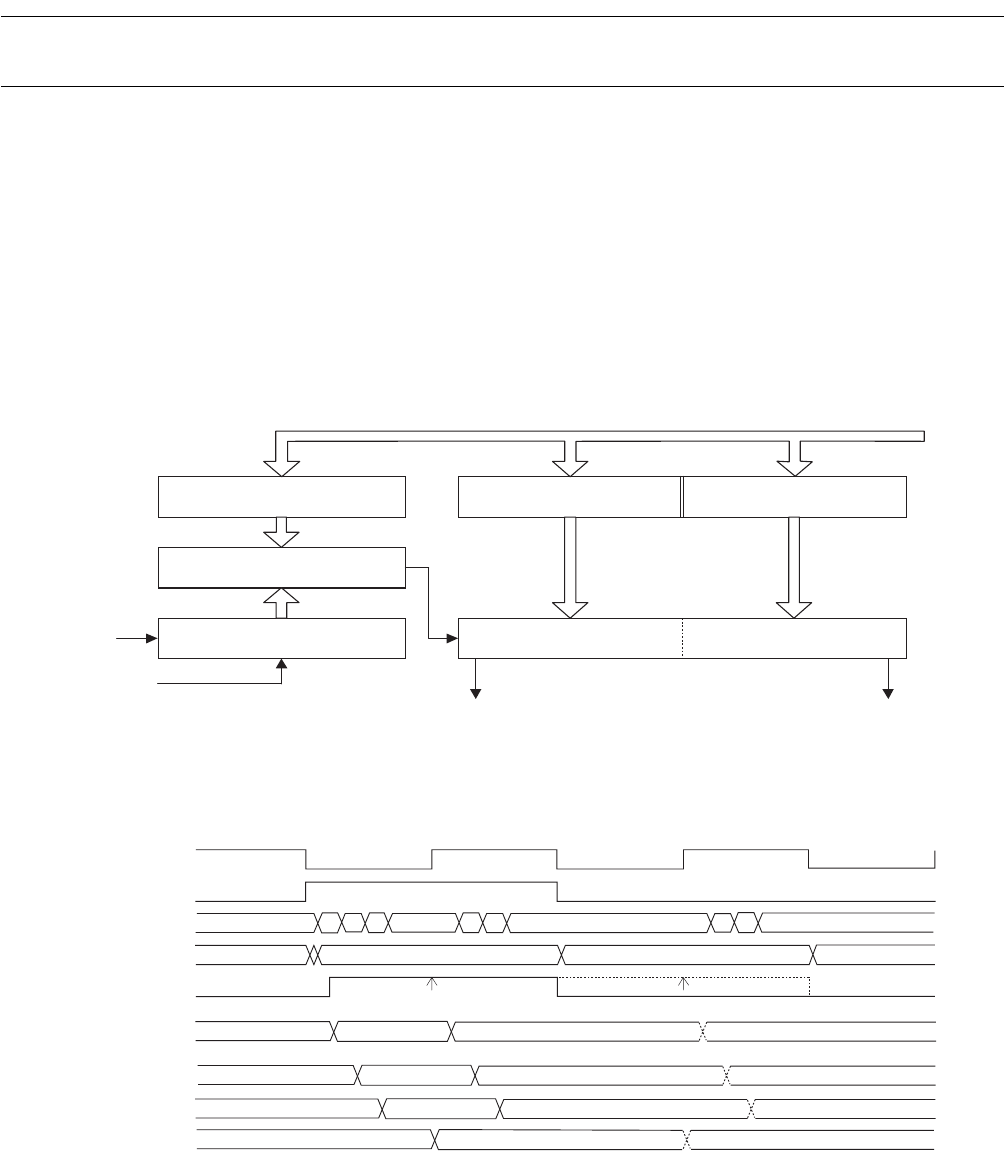

■ Output Operation of PPG

Clears the relative counter when the values set to the timing data register (PPGxTH, PPGxTL) and the FRC

value match, and after loading the value of the address set register to the memory address counter, retains

the 1st field data of data RAM (output timing data, output data) in the output timing data latch and output

data latch.

The retained output data is transferred to the output latch by the rising edge of the relative counter clock

under the cycle whose relative counter and output timing data match, and the 2nd field data is newly

retained in each latch.

Figure 8.5-1 Output operation of PPG

Figure 8.5-2 PPG output detail timing

Output timing data latch

Comparator

Relativity counter

(OTD)

PPG Output

Output latch (OUTH)

Output data latch (ODLH) Output data latch (ODLL)

Output latch (OUTL)

FRC3

FRC.EQ.TD

Data RAM

(FRC3=2

4

/fch, 0.8us:fch=@20MHz)

6543210

X

7 8 9

XXXX 0000 0001 0002

TX (XXXX) T0 (0000) Tn (nnnn)

ODL (Tn)

ODH (Tn)

OUT (T0)OUT (TX-1)

ODL (TX)

ODH (TX) ODH (T0)

ODL (T0)

FRC3

FRC. EQ. TD

RAM Relativity addr

Relativity counter

CNT. EQ. OTD

OTD

ODLH

ODLL

OUTL