68

CHAPTER 3 CPU

3.12.6 Reset Factor Retention

The reset factor retention holds the factor of previous generation. All flag is cleared to

"0" by reading.

Once a factor flag is set, it is not cleared unless the factor is read.

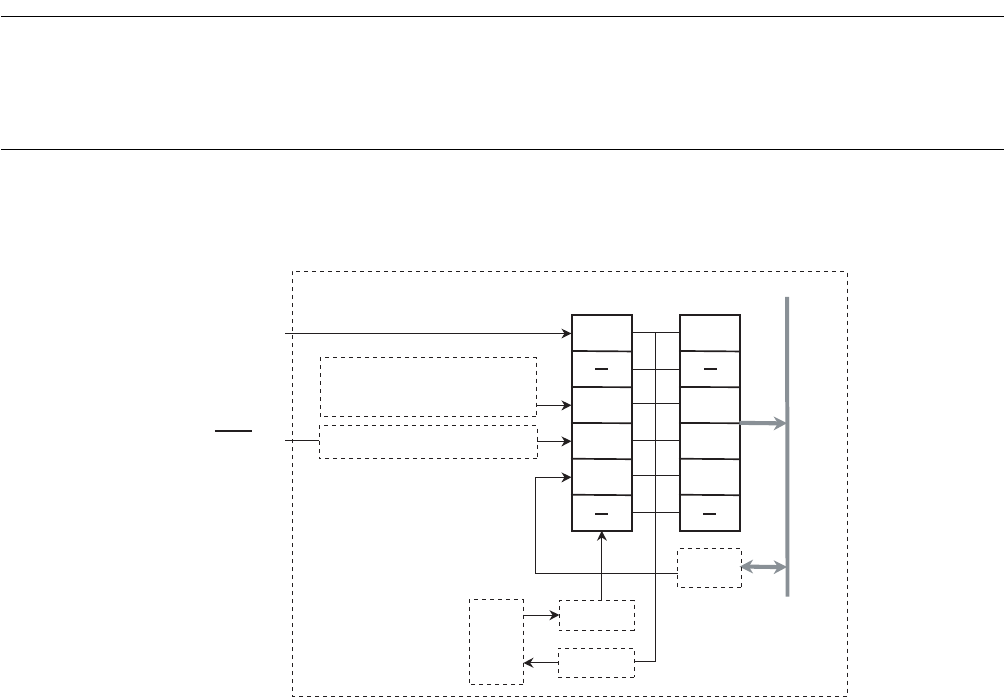

■ Block Diagram of Reset Factor Retention Circuit

Figure 3.12-8 Reset factor circuit Block Diagram

■ Setting of Reset Factor Retention

No special settings are required to use the rest factor function. Commands for reading the reset factor

register and branching to the appropriate program shall be placed near the front of the program to be set in

the reset entry address.

[example]

RESET-ENTRY

LDI:32 #RSRR,R10

LDI:8 #10000000B,R2

LDUB @R10,R1 ; GET RSRR VALUE INTO R1

MOV R1,R10 ; R10 USED AS A TEMPORARY REGISTER

AND R2,R10 ; WAS PONR RESET?

BNE PONR-RESET

LSR #1,R2 ; POINT NEXT BIT

MOV R1,R10 ; R10 USED AS A TEMPORARY REGISTER

AND R2,R10 ; WAS WATCH DOG RESET?

BNE WDOG-RESET

...

RST pin

Internal bus

State

transition

circuit

ERST

PONR

WDOG

SRST

Reset input circuit ERST

PONR

WDOG

SRST

watch-dog Timer

reset detect Circuit

SRST

decoder

.o r.

Power-on

detection