263

18.2 Register of 10-bit General-purpose Prescaler

The register configuration/functions of 10-bit general-purpose prescaler is shown.

■

Prescaler Control Register (GPRC)

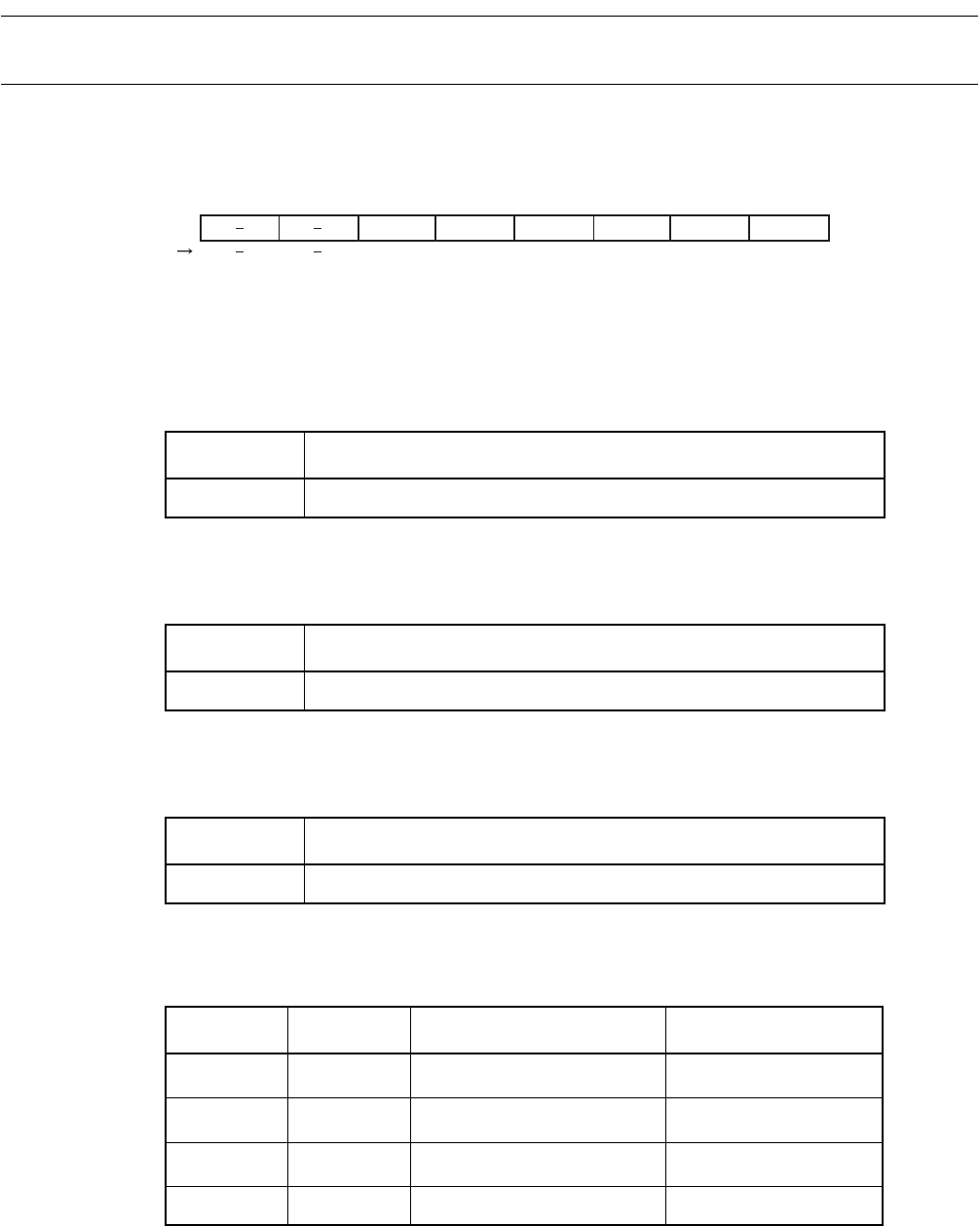

Figure 18.2-1 Prescaler control register (GPRC)

[bit7, 6]:

There are unused bits.

[bit5]:INV

It is external clock input polarity selection bit.

[bit4]:OM

It is output mode selection bit.

[bit3]:LDM

It is update mode selection bit of reload data.

[bit2, 1]:PCS1, 0

There are input clock select bits.

7 6 5 4 3 2 1 0

--XX 0XX0

B

Initial value

bit

Address: 000031

H

Access

INV OM LDM PCS1 PCS0 ST

R/W R/W R/W R/W R/W R/W

0

Input through

1 Input inversion

0

Output reload pulse

1 Two-division output of reload pulse

0

Update by writing data register

1 Update by both edges of PPG0 output (PO015)

PCS1 PCS0 Selection Clock Cycle (fch:@20MHz)

0 0

2

1

/fch (FRC0)

100 ns

0 1

2

3

/fch (FRC2)

400 ns

1 0

2

6

/fch (FRC5)

3.2 us

1 1 External clock (PCK/OSCI) -