169

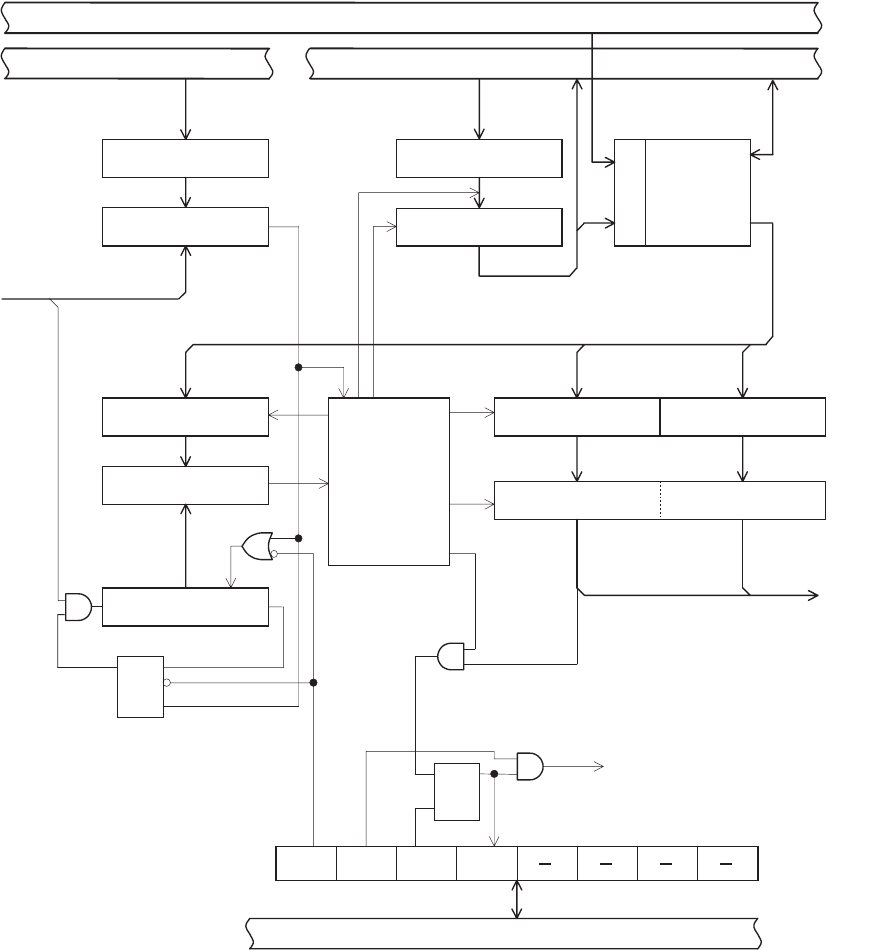

Figure 8.1-2 Block diagram of programmable pulse generator (PPG0, 1)

Q R1

R2

S

Relativity counter

Comparator

Output timing latch

Comparator

Output pattern data latch

Output data latch Output data latch

Address setting

PPGxS A

DataR AM

PPGxTH, L

FRC4-19

FRC3

Internal bus (R-Bus) Internal bus (D-Bus)

Internal bus (Address-Bus)

Timing

control

SQ

R

PPG

output

PPGxC

IFFCLRIEST

IRQx

(to I-unit)

EQ

Load

EQ.STB

PO??

R

Internal bus (AD-Bus)

OVF

Timing data register

Address counter