83

■ Reset Generation Delay

Once the watchdog timer is initiated, A5

H

and 5A

H

must be regularly written to the watchdog reset

postpone register (WPR) by the program.

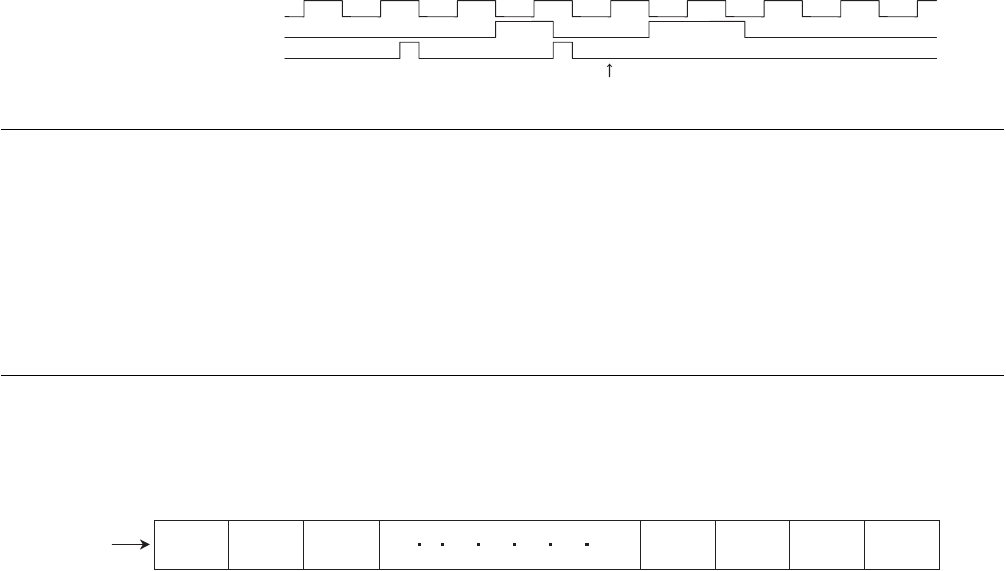

The flip-flop for watchdog reset memorizes the falling edge of the tap selected by the timebase timer if this

flip-flop is not cleared by the 2nd falling edge, a reset is generated.

Figure 3.12-16 shows the operations of the watchdog timer.

Figure 3.12-16 Operations of watchdog timer

Notes:

• The time interval between the first 5A

H

and the next 5A

H

is not specified. Postponement of the

watchdog can be performed only when the interval for 5A

H

writing is within the period specified by the

WT bit twice, and A5

H

writing is performed once between them.

• After the first A5

H

if writing other than 5A

H

is performed, the first A5

H

writing will be invalid.

Therefore, A5

H

must be written again.

■ Timebase Timer

Figure 3.12-17 Configuration of Timebase Timer

The timerbase timer is used as the timer for the clock supplying to the watchdog timer and timer for the

oscillation stabilization wait time. The operation clock φ is twice as large as X0 when GCR CHC is 1, and

is one time as large as X0 when GCR CHC is 0.

Timebase timer Overflow

Watchdog flip-flop

Watchdog start Watchdog clear Watchdog reset generation

WTE write

φ 1/2

1

1/2

2

1/2

3

1/ 2

18

1/2

19

1/2

20

1/2

21