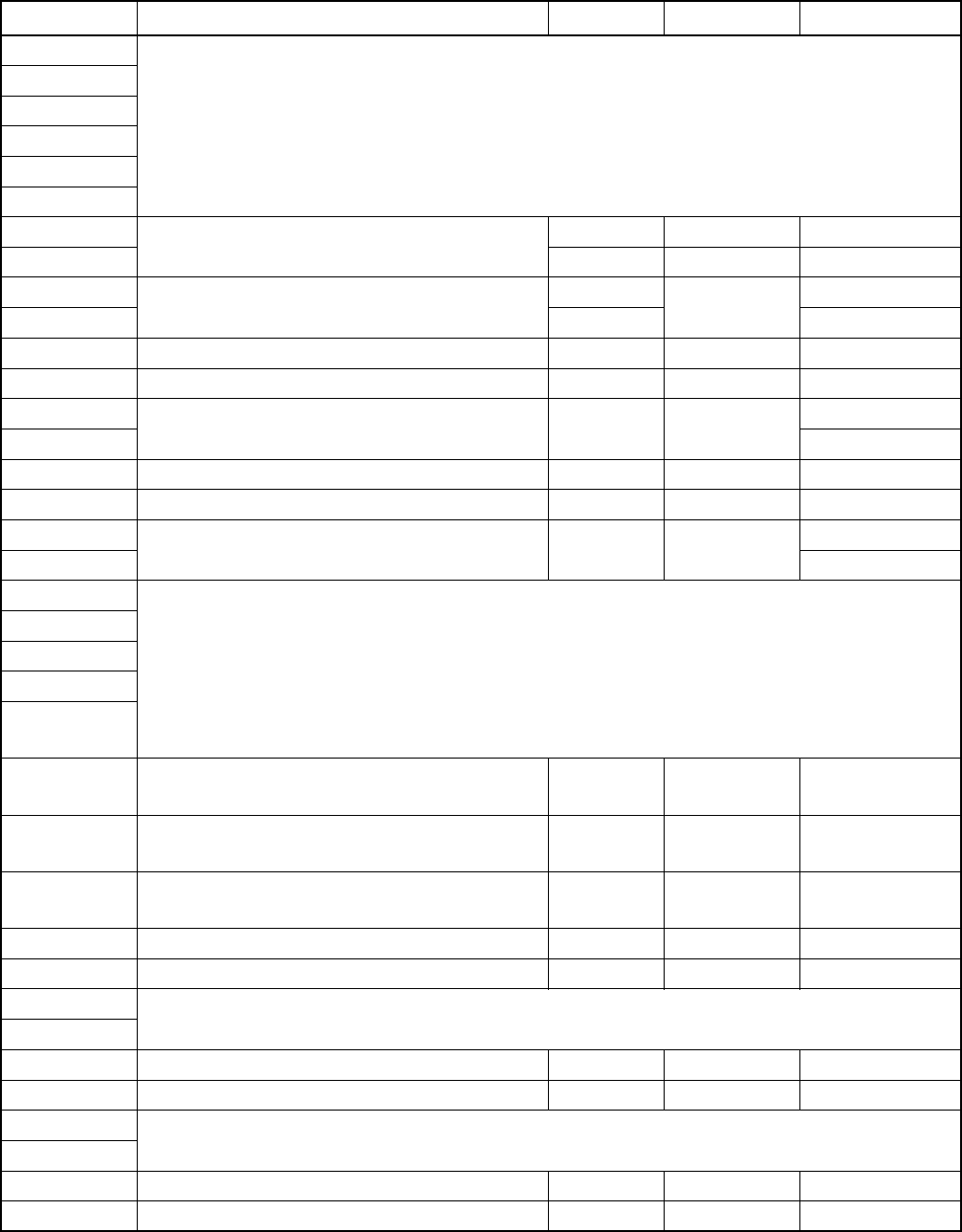

302

Appendix A I/O Map

0009A

H

Reserved

0009B

H

0009C

H

0009D

H

0009E

H

0009F

H

000A0

H

A/DC Control Register

R ADCH

XXX0 0000

B

000A1

H

R ADCL

000- -XXX

B

000A2

H

A/DC Soft conversion analog input selection

register

R/W

SCIS

0000 0000

B

000A3

H

R/W

0000 0000

B

000A4

H

Reserved

000A5

H

Soft conversion Status Register R/W SCSR

X10- -001

B

000A6

H

A/DC Soft conversion FIFO data register R SCFD

XXXX --XX

B

000A7

H

XXXX XXXX

B

000A8

H

Reserved

000A9

H

A/DC Hard conversion Status Register R/W HCSR

X10- -001

B

000AA

H

A/DC Hard conversion FIFO data register R HCFD

XXXX --XX

B

000AB

H

XXXX XXXX

B

000AC

H

Reserved

000AD

H

000AE

H

000AF

H

000B0

H

to

001FF

H

00200

H

to

002FF

H

PPG0 Data RAM R/W -

XXXX XXXX

B

00300

H

to

0037F

H

Serial 0 Data buffer RAM R/W -

XXXX XXXX

B

00380

H

to

003BF

H

PPG1 Data RAM R/W -

XXXX XXXX

B

003C0

H

PPG0 Control Register R/W PPG0C

0000 X100

B

003C1

H

PPG0 start address setting register R/W PPG0SA

XXXX XXXX

B

003C2

H

Reserved

003C3

H

003C4

H

PPG1 Control Register R/W PPG1C

0000 X100

B

003C5

H

PPG1 start address setting register R/W PPG1SA

XXXX XXXX

B

003C6

H

Reserved

003C7

H

003C8

H

Serial control register R/W S0CR

0100 1000

B

003C9

H

Clock Mode setting register R/W S0MR

--0X XXXX

B

Table A-1 I/O Map

Address Register Name Access Register Initial value