172

CHAPTER 8 Programmable Pulse Generator (PPG0, 1)

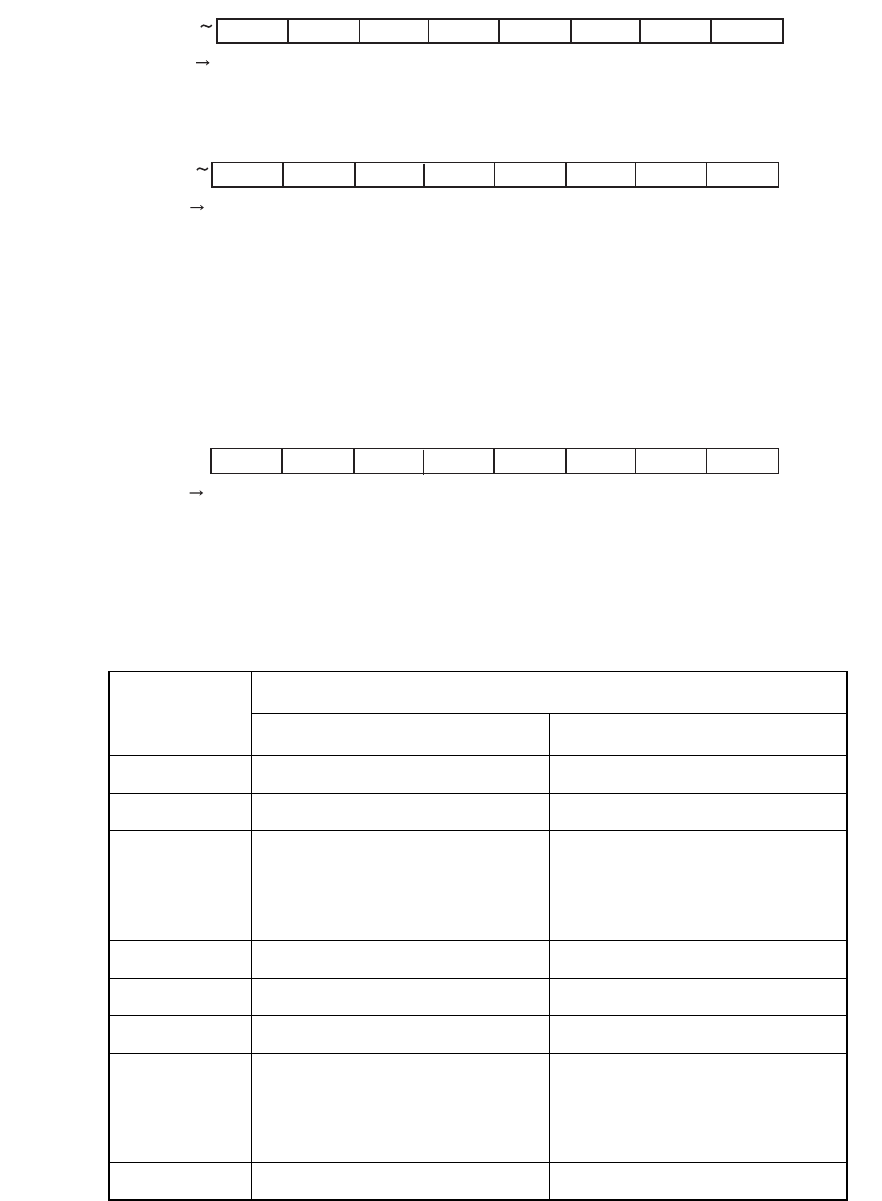

■ Timing Data Register (PPGxT)

Figure 8.2-2 Timing data register (PPGxTH)

Figure 8.2-3 Timing data register (PPGxTL)

When the timing data register is updated continuously, write new data after 18/fch or more has passed after

writing.

Do not use the byte access command to access the register.

■ Start Address Setting Register (PPGxSA)

Figure 8.2-4 Start address setting register (PPGxSA)

[bit7 to 0]:A7 to 0

The set address will be the PPG output starting frame data address, and the read value will be the frame

data address to be output next.

7 6 5 4 3 2 1 0

XXXX XXXX

B

Initial value

bit

D15 D14 D13 D12 D11 D10 D09 D08

WWWWWWWW

Address: 00006C

H

(PPG0TH)

00006E

H

(PPG1TH)

Access

7 6 5 4 3 2 1 0

XXXX XXXX

B

Initial value

bit

D07 D06 D05 D04 D03 D02 D01 D00

WWWWWWWW

Address: 00006D

H

(PPG0TL)

00006F

H

(PPG1TL)

Access

7 6 5 4 3 2 1 0

XXXX XXXX

B

Initial value

bit

Address: 0003C1

H

(PPG0SA)

0003C5

H

(PPG1SA)

R/W R/W R/W R/W R/W R/W R/W R/W

A7/SA7

A6/SA6

A5/SA5

A4/SA4

A3/SA3

A2/SA2

A1/SA1

A0/SA0

Access

Table 8.2-1 Relationship between start address and data RAM

Set value

Data RAM Address

PPG0 PPG1

00

H

000200

H

000380

H

02

H

000202

H

000382

H

04

H

000204

H

000384

H

to to

3C

H

00023C

H

0003BC

H

3E

H

00023E

H

0003BE

H

40

H

000240

H

-

42

H

000242

H

-

44

H

000244

H

to to -

FC

H

0002FC

H

FE

H

0002FE

H

-