165

7.3 Operation of FRC Capture

Up to eight capture data can be fetched in FIFO. If a new capture request is generated

while data is full, the former data will be updated with the new data.

If a capture request is generated while the FIFO storage is empty, overhead for a

maximum of "fch x 18 cycles" (10 cycles from the CIF set) will be generated until data

setup (readable status).

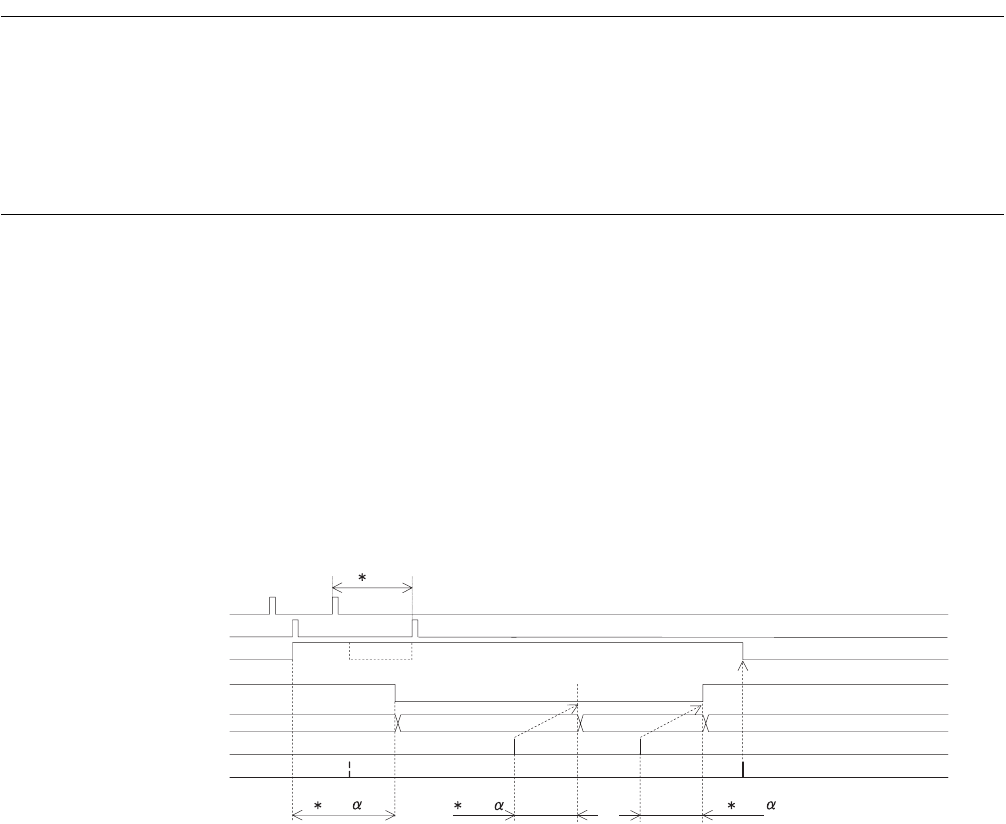

■ Controlling Method of FIFO

Latching the data in FIFO is performed the following procedure.

1. When EMP bit is "0", read the data.

2. Writes the INC bit to "1". Therefore, next data in FIFO is ready. (Maximum of fch x 5 cycles)

3. Checks the EMP bit and EMP=0: Returns to 2) to extract the following data. EMP=1: Completes all

data reading.

To initialize FIFO and dispose of data within FIFO storage, writing "1" to the FIFO clear bit initializes the

FIFO.

Figure 7.3-1 Operation timing diagram of FIFO

■ Capture Data

The lowest 3 bits of the capture data will be valid only when the DFG bit of the capture source register is

"1". When the DFG bit is "0", masks the lowest 3 bits after reading the capture data.

■ Reading of FRC Count Data

Use the word access command to read the counter data. When the half-word access command is read, after

reading the counter data subordinate, read the superior data.

Correct values cannot be read using byte access commands. The top byte read by the word access

command is invalid data, so execute mask processing.

FCLR_bit Write

INC_bit Write

Captuer request

Captuer Timing

CIF_bit

EMP_bit

Fifo Data

8 fch

8 fch+ 3 fch+ 3 fch+