124

CHAPTER 5 I/O Port

■ Registers for Port 2, 3

●

Port 2, 3 data register (PDR2, 3)

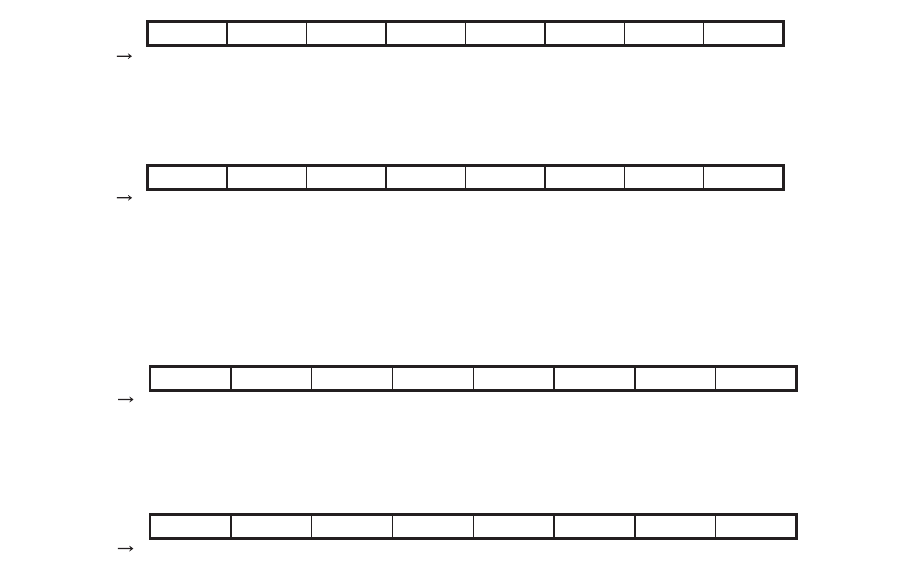

Figure 5.4-2 Port 2 data register (PDR2)

Figure 5.4-3 Port 3 data register (PDR3)

●

Port 2, 3 direction register (DDR2, 3)

Figure 5.4-4 Port 2 direction register (DDR2)

Figure 5.4-5 Port 3 direction register (DDR3)

7 6 5 4 3 2 1 0

XXXX XXXX

B

Initial value

bit

R/W R/W R/W R/W R/W R/W R/W R/W

PD27 PD26 PD25 PD24 PD23 PD22 PD21 PD20

Access

Address: 000001

H

7 6 5 4 3 2 1 0

XXXX XXXX

B

Initial value

bit

R/W R/W R/W R/W R/W R/W R/W R/W

PD37 PD36 PD35 PD34 PD33 PD32 PD31 PD30

Access

Address: 000000

H

7 6 5 4 3 2 1 0

0000 0000

B

Initial value

bit

DR27 DR26 DR25 DR24 DR23 DR22 DR21 DR20

WWWWWWWW

Access

Address: 000009

H

7 6 5 4 3 2 1 0

0000 0000

B

Initial value

bit

DR37 DR36 DR35 DR34 DR33 DR32 DR31 DR30

WWWWWWWW

Access

Address: 000008

H