191

*:fch: source oscillation frequency

[bit0]:TSTR

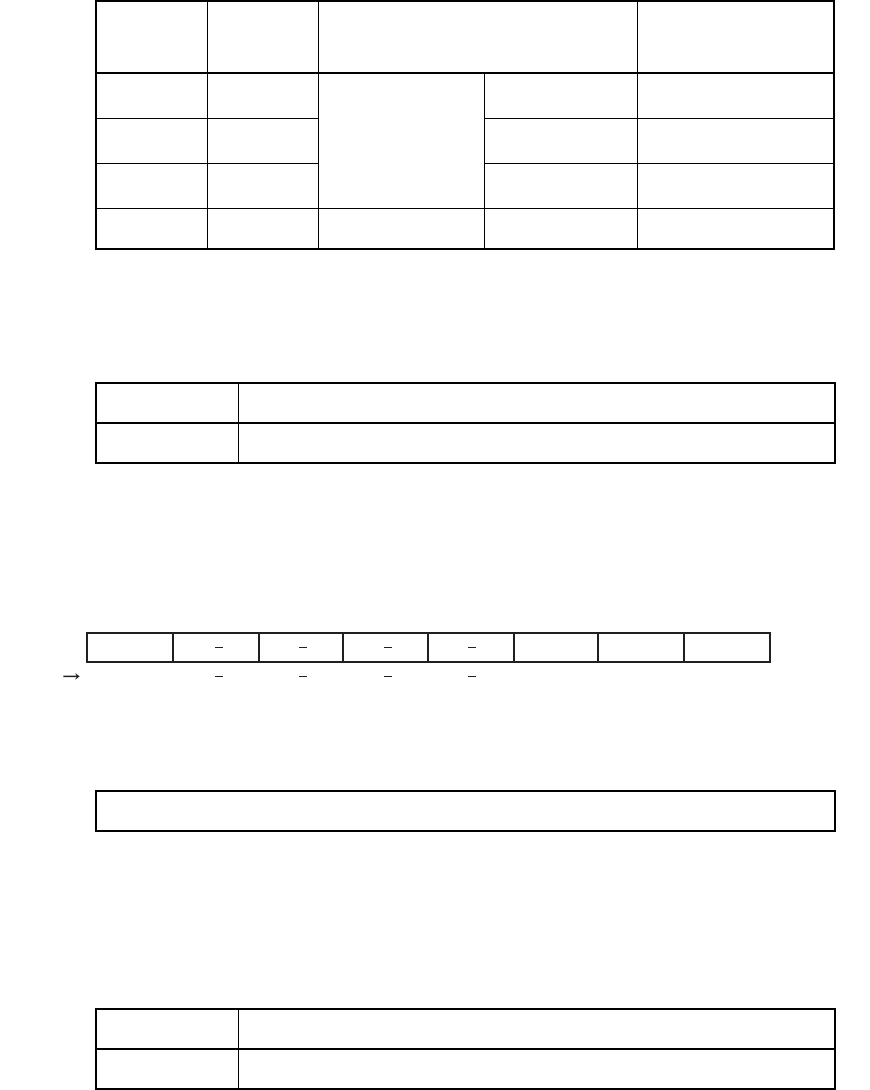

■ Timer Control Register H (TxCRH)

Figure 10.3-2 Timer control register H (TxCRH)

[bit7]:Test

It is for a test.

[bit6-3]:

It is an unused bit.

[bit2]:FCLR

It is match detection flag clear bit.

Always read "1" at reading.

Table 10.3-2 Timer 4

TC1 TC0 Selection Clock

Clock cycle time

(fch:@20 MHz)

0 0

Internal clock

2

4

/fch (FRC3)

0.8 µs

0 1

2

6

/fch (FRC5)

3.2 µs

1 0

2

8

/fch (FRC7)

12.8 µs

1 1 External clock EC4 Min ***** µs

Table 10.3-3 Timer operation enable bit

0 Timer operation stop

1 Enabling timer Operation

7 6 5 4 3 2 1 0

0--- -1X0

B

Initial value

bit

Test FCLR IFLG TIE

R/W

R/W R/WR

Access

Always write "0" to this bit.

0 Clear match detection flag.

1 None