254

CHAPTER 17 Serial I/O

[bit3]:IC0

It is selection bit of interval. Setting the interval is as follows.

*:Tclk= Shift clock cycle time

[bit2]:SC2

[bit1]:SC1

[bit0]:SC0

It is selection bit of shift clock.

φ: Defined by peripheral clock gear (PCK1 and 0)

fch: Source oscillation frequency

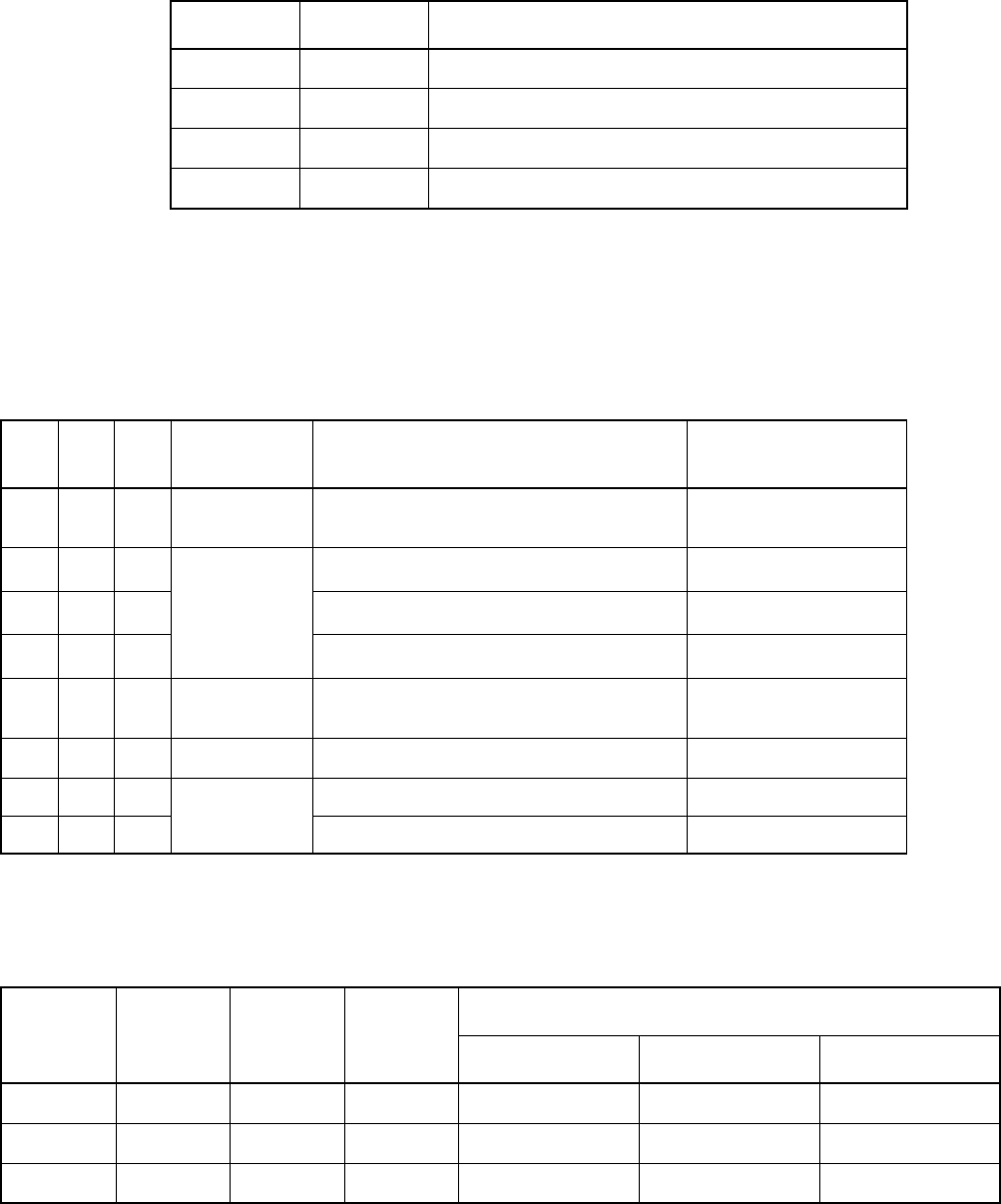

IC1 IC0 Interval: T int

0 0 Tclk × 16 µs

0 1 Tclk × 32 µs

1 0 Tclk × 64 µs

1 1 No interval time (selection is disabled at external clock)

SC2 SC1 SC0 Selection clock Shift clock cycle time: Tclk

Cycle time

(fch=@20MHz)

000

Specification

prohibited

--

001

Internal clock

2

3

× φ

0.4

µs

(1:1)

010

2

4

× φ

0.8

µs

(1:1)

011

2

5

× φ

1.6

µs

(1:1)

100

Specification

prohibited

--

101External clock

Min 8 x

φ

(duty 50%) 0.4

µs

(

φ

:50 ns)

110

Specification

prohibited

--

111 - -

Table 17.2-1 Shift clock cycle and interval at 20 MHz operation

SC2 SC1 SC0 Tclk

Tint

IC1, IC0=(0, 0) IC1, IC0=(0, 1) IC1, IC0=(1, 0)

0 0 1 0.4

µs6.4

µs 12.8

µs 51.2

µs

0 1 0 0.8

µs 12.8

µs 25.6

µs 102.4

µs

0 1 1 1.6

µs 25.6

µs 51.2

µs 204.8

µs