321

■

The Other Instruction

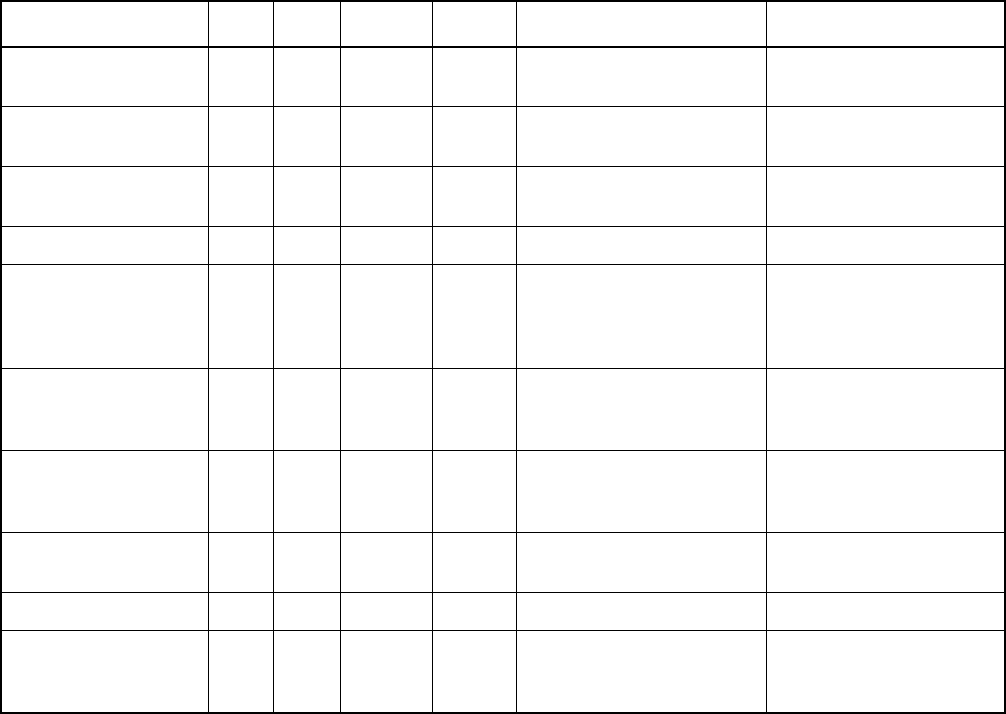

Table E-15 The other Instruction

Mnemonic Type OP CYCLE NZVC Operation Remark

NOP E 9F-A 1 ---- Anything does not change

either.

ANDCCR #u8

ORCCR #u8

D

D

83

93

c

c

CCCC

CCCC

CCR and u8 →

CCR

CCR or u8 →

CCR

STILM #u8 D 87 1 ---- i8→

ILM Value set of ILM

immediately

ADDSP #s10

*1

D A3 1 ---- R15+=s10 ADDSP Instruction

EXTSB Ri

EXTUB Ri

EXTSH Ri

EXTUH Ri

E

E

E

E

97-8

97-9

97-A

97-B

1

1

1

1

----

----

----

----

sign extension 8

→

32bit

0 expansions 8→

32bit

sign extension16

→

32bit

0 expansions16→

32bit

LDM0 (reglist)

LDM1 (reglist)

*LDM (reglist)

*2

D

D

8C

8D

----

----

----

(R15)

→

reglist, R15 increment

(R15) →

reglist, R15 increment

(R15) →

reglist, R15 increment

loading multi R0 - R7

loading multi R8 - R15

loading multi R0 - R15

STM0 (reglist)

STM1 (reglist)

*STM (reglist)

*3

D

D

8E

8F

----

----

----

R15 decrement, reglist

→

(R15)

R15 decrement, reglist→

(R15)

R15 decrement, reglist

→

(R15)

store multi R0 - R7

store multi R8 - R15

store multi - R0 - R15

ENTER #u10

*4

D 0F 1+a ---- R14

→

(R15-4), R15-4

→

R14,

R15-u10

→

R15

Entrance processing of

function

LEAVE E 9F-9 b ---- R14+4

→

R15, (R15-4)

→

R14 Exit processing of function

XCHB @Rj,Ri A 8A 2a ---- Ri→

TEMP

(Rj)→

Ri

TEMP

→

(Rj)

For semaphore control

Byte Data

*1: s10 is set by that assembler calculates s10/4 to s8. s10 has the sign.

*2: Under the reglist, if one of R0-R7 is specified, LDM0 is generated, whereas if one of R8-R15 is specified, LDM1 is generated. In

other case, both LDM0 and LDM1 may be able to be generated.

*3: Under the reglist, if one of R0-R7 is specified, STM0 is generated, whereas if one of R8-R15 is specified, STM1 is generated. There

is a case generating both STM1 and STM0.

*4: u10 is set by that assembler calculates u10/4 to u8. u10 does not have the sign.