215

12.3 Operation of 8-bit Pulse Width Counter

The pulse width counting operation of the 8-bit pulse width counter is described.

■ Pulse Input Mask Function

Pulse input (PMI) can be directly masked by the pulse mask input signal (PMSK).

In order to control PMI input by PMSK input, set "1" to the mask input enabled (MSKE) bit of the PWC

control register (PWCC) for PMSK input enabled status. Therefore, the PMI input can be controlled by the

PMSK input signal.

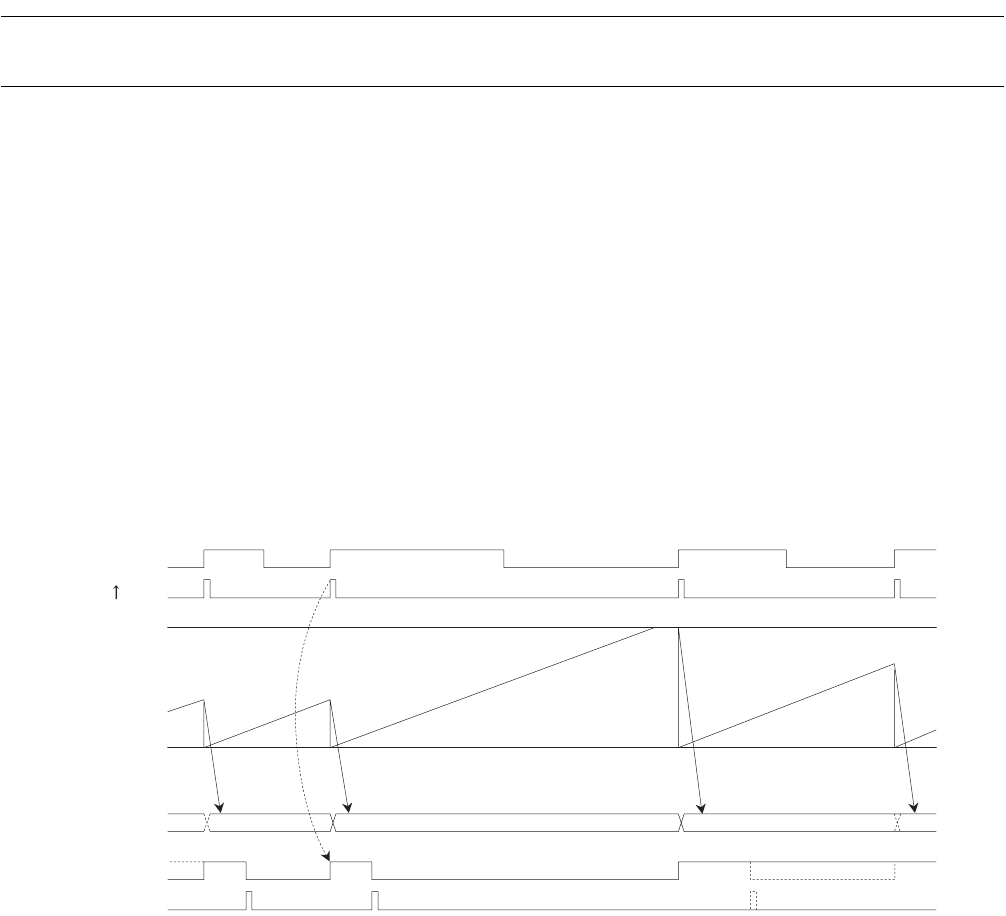

■ Pulse Width Count Operation

The PWC clears the counter value capture and counter at the rising edge of the PMI signal. The cleared

counter continues the counting operation as it is, and when the counter value becomes "FF

H

", counting

stops, and retains that status until detecting the rising edge of the next PMI input.

In terms of the capture operation, when the capture flag (CAPF) is "0" (enabled status), capture is executed,

whereas when CAPF is "1" (disabled status), capture is not executed. These operation shows in Figure

12.3-1 .

Figure 12.3-1 PWC operation

■ CAPF Bit

The PWC initializes the CAPF bit to "1", when the ST bit is "0". In this case, do not clear the CAPF bit

during the operation is stopped.

Clearing the CAPF bit must be executed after enabling the PWC operation.

PMI Input

Edge

PWCD

CAPF

CAPE

Write

FF

H

nn

H

xx

H

CAP.Enable

CAP.Disable

00H

FFH

Count value