233

15.3 Operation of Interrupt Controller

The interrupt request generated at the resource is controlled by the interrupt-enabled

bit that has been set per resource. If an interrupt is enabled at each resource, the

generated interrupt request generates an interrupt request signal to the interrupt

controller.

■ Priority Order Evaluation

The interrupt controller selects the highest priority factor from those that have been generated

simultaneously, and outputs the factor's interrupt level and interrupt number to the CPU.

The criteria for evaluating the priority order of the interrupt causes are shown below.

●

The interrupt cause meets the following conditions:

• The interrupt cause has an interrupt level other than 31 (A value of 31 represents interrupt disable.)

• The interrupt cause has the lowest interrupt level

• The interrupt cause has the smallest interrupt number

Table 15.3-1 shows the relationship between interrupt causes, interrupt numbers, and interrupt levels.

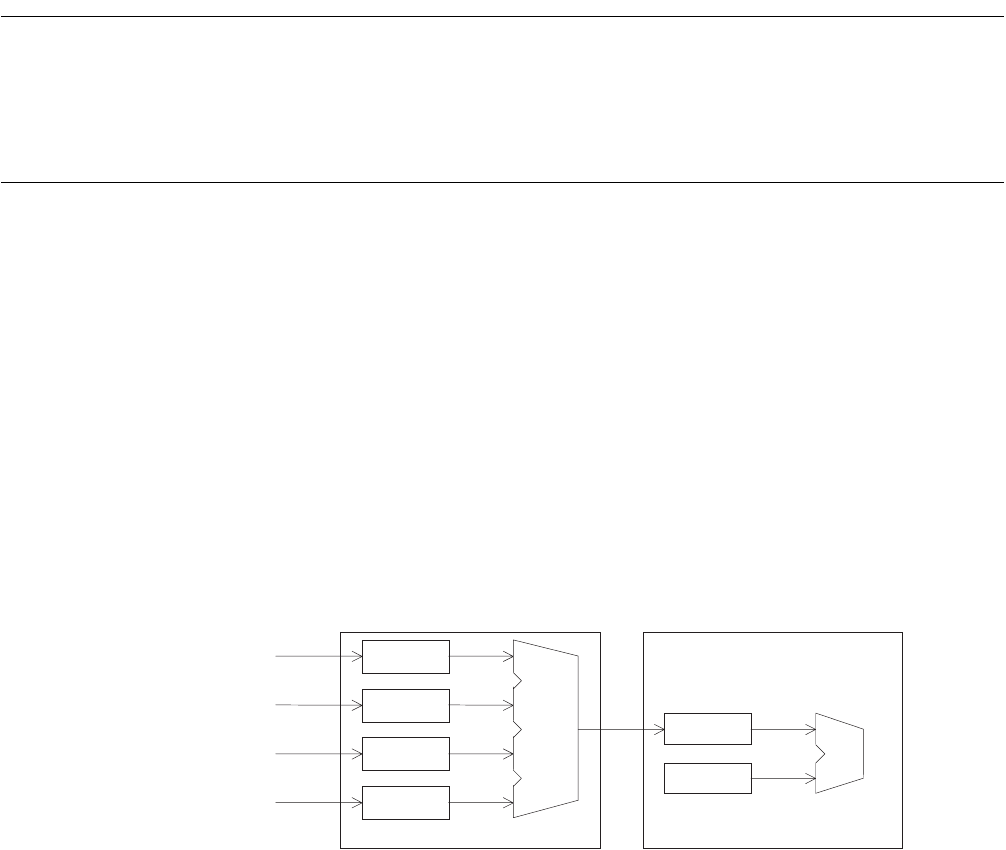

Figure 15.3-1 Flowchart of interrupt cause

Interrupt Controler CPU

Resource request 01 ICR01

Resource request 02 ICR02

CMP IL

Resource request xx ICRxx

CMP

ILM

Resource request yy ICRyy