325

■

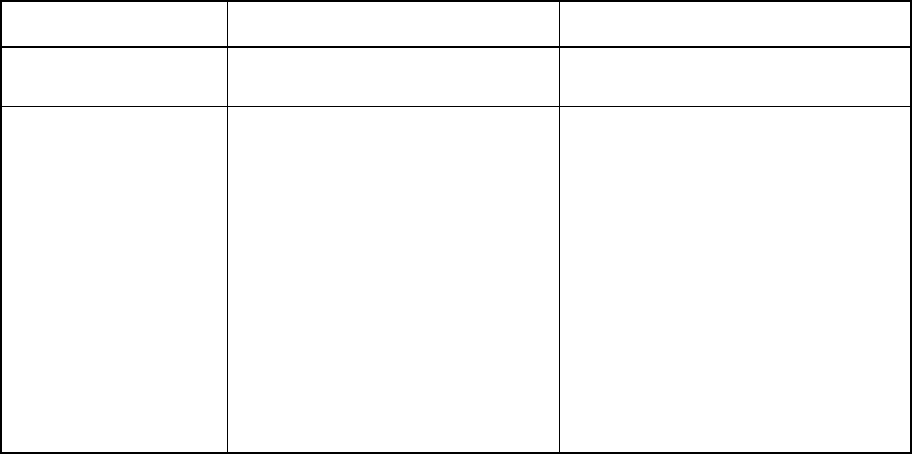

32-bit Delayed Divergence Macro Instruction

Table E-19 32-bit Delayed divergence macro instruction

Mnemonic Operation Remark

*CALL32:D label32,Ri Address of the following instruction

+2

→

RP, label32

→

PC

Ri: Temporary register (Refer to reference 1.)

*BRA32:D label32,Ri

*BEQ32:D label32,Ri

*BNE32:D label32,Ri

*BC32:D label32,Ri

*BNC32:D label32,Ri

*BN32:D label32,Ri

*BP32:D label32,Ri

*BV32:D label32,Ri

*BNV32:D label32,Ri

*BLT32:D label32,Ri

*BGE32:D label32,Ri

*BLE32:D label32,Ri

*BGT32:D label32,Ri

*BLS32:D label32,Ri

*BHI32:D label32,Ri

label32

→

PC

if(Z==1)thenlabel32→

PC

↑

s/Z==0

↑

s/C==1

↑

s/C==0

↑

s/N==1

↑

s/N==0

↑

s/V==1

↑

s/V==0

↑

s/VxorN==1

↑

s/VxorN==0

↑

s/(VxorN)orZ==1

↑

s/(VxorN)orZ==0

↑

s/CorZ==1

↑

s/CorZ==0

Ri: Temporary register (Refer to reference 2.)

Ri: Temporary register (Refer to reference 3.)

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

↑

Reference 1: CALL32:D

1) When label32-PC-2 is -0x800 - +0x7fe, the instruction is generated as follows.

CALL:D label12

2) When label32-PC-2 is outside the area as per 1) and includes an external reference symbol, the command is generated as

follows.

LDI:32 #label32,Ri

CALL:D @Ri

Reference 2: BRA32:D

1) When label32-PC-2 is - 0x100 - + 0xfe, the instruction is generated as follows.

BRA:D label9

2) When label32-PC-2 is outside the area as per 1) and includes an external reference symbol, the command is generated as

follows.

LDI:32 #label32,Ri

JMP:D @Ri

Reference 3: Bcc32:D

1) When label32-PC-2 is - 0x100 - + 0xfe, the instruction is generated as follows.

Bcc:D label9

2) When label32-PC-2 is outside the area as per 1) and includes an external reference symbol, the command is generated as

follows.

Bxcc false xcc is a contradiction condition of cc.

LDI:32 #label32,Ri

JMP:D @Ri

false: