62

CHAPTER 3 CPU

Note: φ is twice as large as X0 when GCR CHC is 1, and is one time as large as X0 when GCR CHC is 0.

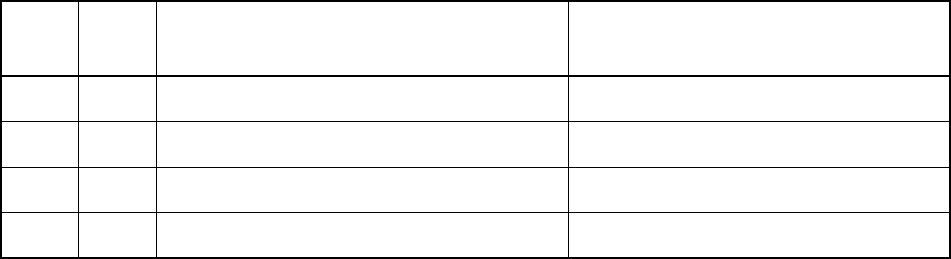

Table 3.12-1 Watchdog timer cycle specified by WT1 and WT0

WT1 WT0

Writing spacing to at least necessary for

control generation of watchdog reset WPR

Timer from last 5A

H

write to WPR to

occurrence of watchdog resetting

0 0

φ × 2

15

(Initial value) φ × 2

15

to φ × 2

16

0 1

φ × 2

17

φ × 2

17

to φ × 2

18

1 0

φ × 2

19

φ × 2

19

to φ × 2

20

1 1

φ × 2

21

φ × 2

21

to φ × 2

22