315

■

Addition and Subtraction Instruction

■

Comparison Operation Instruction

■

Logical Operation Instruction

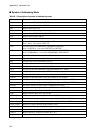

Table E-3 Addition and subtraction instruction

Mnemonic Type OP CYCLE NZVC Operation Remark

ADD Rj, Ri

*ADD #s5, Ri

ADD #u4, Ri

ADD2 #u4, Ri

A

C'

C

C

A6

A4

A4

A5

1

1

1

1

CCCC

CCCC

CCCC

CCCC

Ri+Rj

→

Ri

Ri+s5 →

Ri

Ri+extu(i4)

→

Ri

Ri+extu(i4) →

Ri

Upper in assembler

1 bit is regarded as a sign.

0 expansions

Minus expansion

ADDC Rj, Ri A A7 1 CCCC Ri+Rj +c→

Ri Addition with carry

ADDN Rj, Ri

*ADDN #s5, Ri

ADDN #u4, Ri

ADDN2 #u4, Ri

A

C'

C

C

A2

A0

A0

A1

1

1

1

1

----

----

----

----

Ri+Rj

→

Ri

Ri+s5

→

Ri

Ri+extu(i4)

→

Ri

Ri+extu(i4) →

Ri

Upper in assembler

1 bit is regarded as a sign.

0 expansions

Minus expansion

SUB Rj, Ri A AC 1 CCCC RiRj

→

Ri

SUBC Rj, Ri A AD 1 CCCC RiRj c→

Ri Reduction with carry

SUBN Rj, Ri A AE 1 ---- Ri-Rj

→

Ri

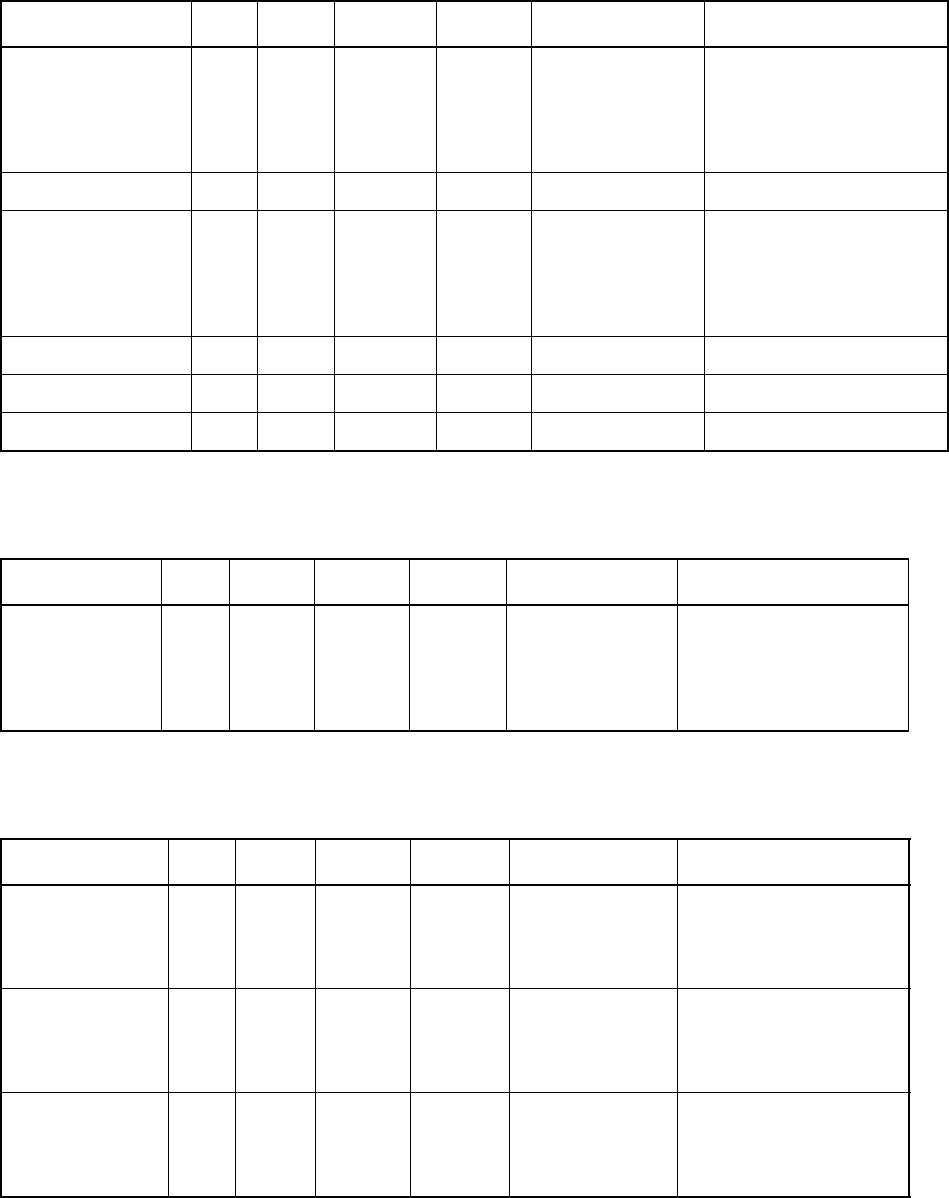

Table E-4 Comparison operation instruction

Mnemonic Type OP CYCLE NZVC Operation Remark

CMP Rj, Ri

*CMP #s5, Ri

CMP #u4, Ri

CMP2 #u4, Ri

A

C'

C

C

AA

A8

A8

A9

1

1

1

1

CCCC

CCCC

CCCC

CCCC

Ri-Rj

Ri-s5

Ri-extu(i4)

Ri-extu(i4)

Upper in assembler

1 bit is regarded as a sign.

0 expansions

Minus expansion

Table E-5 Logical operation instruction

Mnemonic Type OP CYCLE NZVC Operation Remark

AND Rj, Ri

AND Rj, @Ri

ANDH Rj, @Ri

ANDB Rj, @Ri

A

A

A

A

82

84

85

86

1

1+2a

1+2a

1+2a

CC--

CC--

CC--

CC--

Ri &=Rj

(Ri) &=Rj

(Ri) &=Rj

(Ri) &=Rj

Word

Word

Half word

Byte

OR Rj, Ri

OR Rj, @Ri

ORH Rj, @Ri

ORB Rj, @Ri

A

A

A

A

92

94

95

96

1

1+2a

1+2a

1+2a

CC--

CC--

CC--

CC--

Ri | =Rj

(Ri) | =Rj

(Ri) | =Rj

(Ri) | =Rj

Word

Word

Half word

Byte

EOR Rj, Ri

EOR Rj, @Ri

EORH Rj, @Ri

EORB Rj, @Ri

A

A

A

A

9A

9C

9D

9E

1

1+2a

1+2a

1+2a

CC--

CC--

CC--

CC--

Ri ^ =Rj

(Ri) ^ =Rj

(Ri) ^ =Rj

(Ri) ^ =Rj

Word

Word

Half word

Byte