S3F80JB INTERRUPT STRUCTURE

5-9

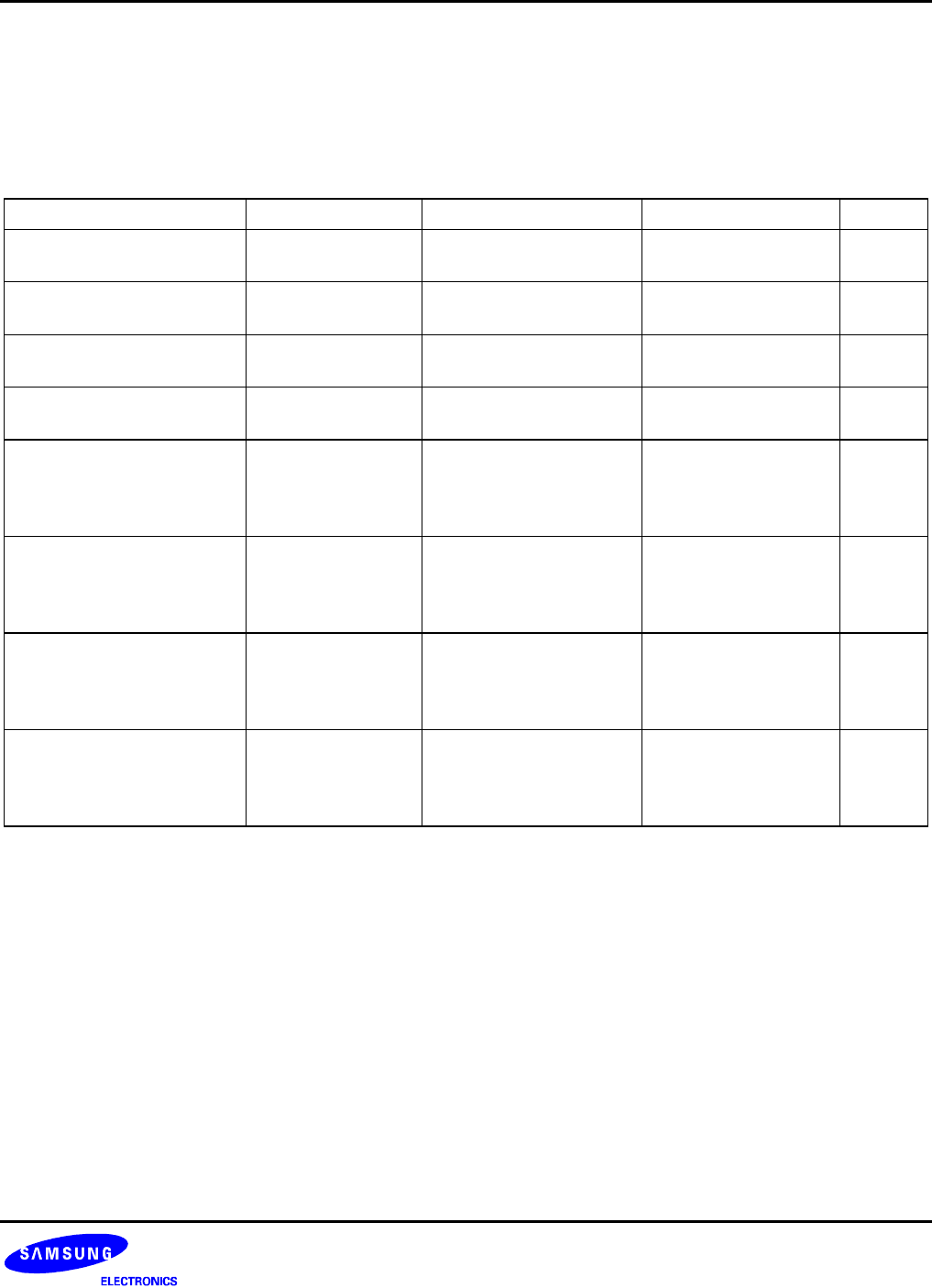

PERIPHERAL INTERRUPT CONTROL REGISTERS

For each interrupt source there is one or more corresponding peripheral control registers that let you control the

interrupt generated by that peripheral (See Table 5-3).

Table 5-3. Vectored Interrupt Source Control and Data Registers

Interrupt Source Interrupt Level Register(s) Location(s) in Set 1 Bank

Timer 0 match/capture or

Timer 0 overflow

IRQ0 T0CON (see Note)

T0DATA

D2H

D1H

Bank0

Timer 1 match/capture or

Timer 1 overflow

IRQ1 T1CON (see Note)

T1DATAH, T1DATAL

FAH

F8H, F9H

Bank0

Counter A IRQ2 CACON

CADATAH, CADATAL

F3H

F4H, F5H

Bank0

Timer 2 match/capture or

Timer 2 overflow

IRQ3 T2CON (see Note)

T2DATAH, T2DATAL

E8H

E6H, E7H

Bank1

P0.7 external interrupt

P0.6 external interrupt

P0.5 external interrupt

P0.4 external interrupt

IRQ7 P0CONH

P0INT

P0PND

E8H

F1H

F2H

Bank0

P0.3 external interrupt

P0.2 external interrupt

P0.1 external interrupt

P0.0 external interrupt

IRQ6 P0CONL

P0INT

P0PND

E9H

F1H

F2H

Bank0

P2.7 external interrupt

P2.6 external interrupt

P2.5 external interrupt

P2.4 external interrupt

IRQ5 P2CONH

P2INT

P2PND

ECH

E5H

E6H

Bank0

P2.3 external interrupt

P2.2 external interrupt

P2.1 external interrupt

P2.0 external interrupt

IRQ4 P2CONL

P2INT

P2PND

EDH

E5H

E6H

Bank0

NOTES:

1. Because the timer 0,timer1 and timer 2 overflow interrupts are cleared by hardware, the T0CON, T1CON and

T2CON registers control only the enable/disable functions. The T0CON, T1CON and T2CON registers contain

enable/disable and pending bits for the timer 0, timer1 and timer2 match/capture interrupts, respectively.

2. If a interrupt is un-mask(Enable interrupt level) in the IMR register, the pending bit and enable bit of the interrupt

should be written after a DI instruction is executed.