S3F80JB ADDRESS SPACES

2-3

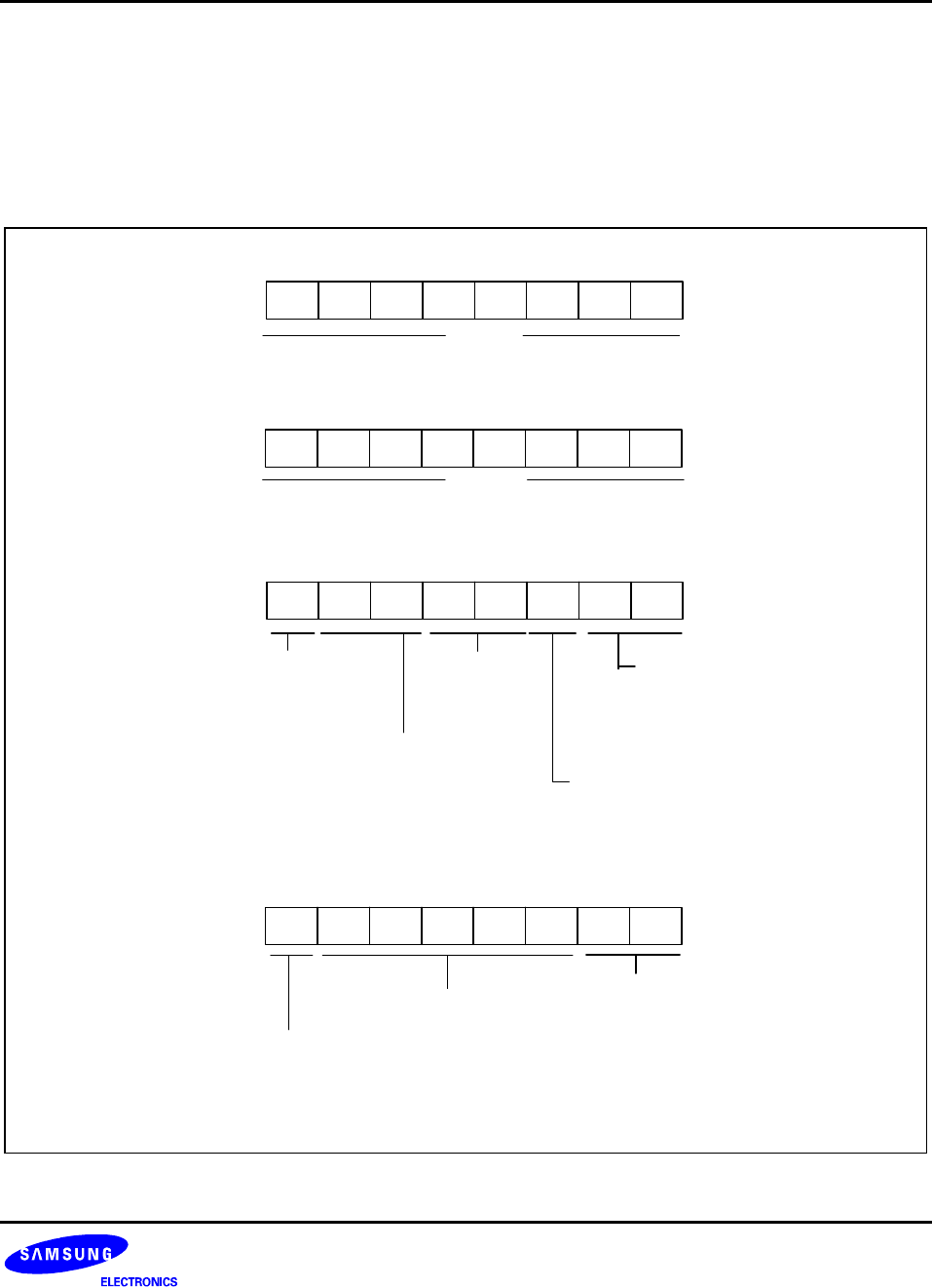

SMART OPTION

Smart option is the program memory option for starting condition of the chip. The program memory addresses

used by smart option are from 003CH to 003FH. The S3F80JB only use 003EH and 003FH. User can write any

value in the not used addresses (003CH and 003DH). The default value of smart option bits in program memory is

0FFH (IPOR disable, LVD enable in the stop mode, Normal reset vector address 100H, ISP protection disable).

Before execution the program memory code, user can set the smart option bits according to the hardware option

for user to want to select.

.7 .6 .5 .4 .3 .2 .1 .0MSB LSB

ROM Address: 003FH

IPOR / LVD Control Bit

0 = IPOR enable

LVD disable in the stop mode

(5)

1 = IPOR disable

LVD enable in the stop mode

(6)

Not used

Frequency Selection Bits

(7)

:

Operating Frequency Range

111110 = 1MHz ~ 4MHz

11111 = 1MHz ~ 8MHz

ISP Reset Vector Address Selection Bits:

(2)

00 = 200H (ISP Area size: 256 bytes)

01 = 300H (ISP Area size: 512 bytes)

10 = 500H (ISP Area size: 1024 bytes)

11 = 900H (ISP Area size: 2048 bytes)

ROM Address: 003EH

ISP Protection Size

Selection Bits:

(4)

00 = 256 bytes

01 = 512 bytes

10 = 1024 bytes

11 = 2048 bytes

.7 .6 .5 .4 .3 .2 .1 .0MSB LSB

ISP Protection Enable/Disable Bit:

(3)

0 = Enable (Not erasable)

1 = Disable (Erasable)

ISP Reset Vector Change Selection Bit:

(1)

0 = OBP Reset vector address

1 = Normal vector (address 100H)

Not used

Not used

ROM Address: 003DH

.7 .6 .5 .4 .3 .2 .1 .0MSB LSB

ROM Address: 003CH

.7 .6 .5 .4 .3 .2 .1 .0MSB LSB

Not used

Figure 2-2. Smart Option