INSTRUCTION SET S3F80JB

6-84

TCM — Test Complement Under Mask

TCM dst,src

Operation: (NOT dst) AND src

This instruction tests selected bits in the destination operand for a logic one value. The bits to be

tested are specified by setting a "1" bit in the corresponding position of the source operand

(mask). The TCM statement complements the destination operand, which is then ANDed with the

source mask. The zero (Z) flag can then be checked to determine the result. The destination and

source operands are unaffected.

Flags: C: Unaffected.

Z: Set if the result is "0"; cleared otherwise.

S: Set if the result bit 7 is set; cleared otherwise.

V: Always cleared to "0".

D: Unaffected.

H: Unaffected.

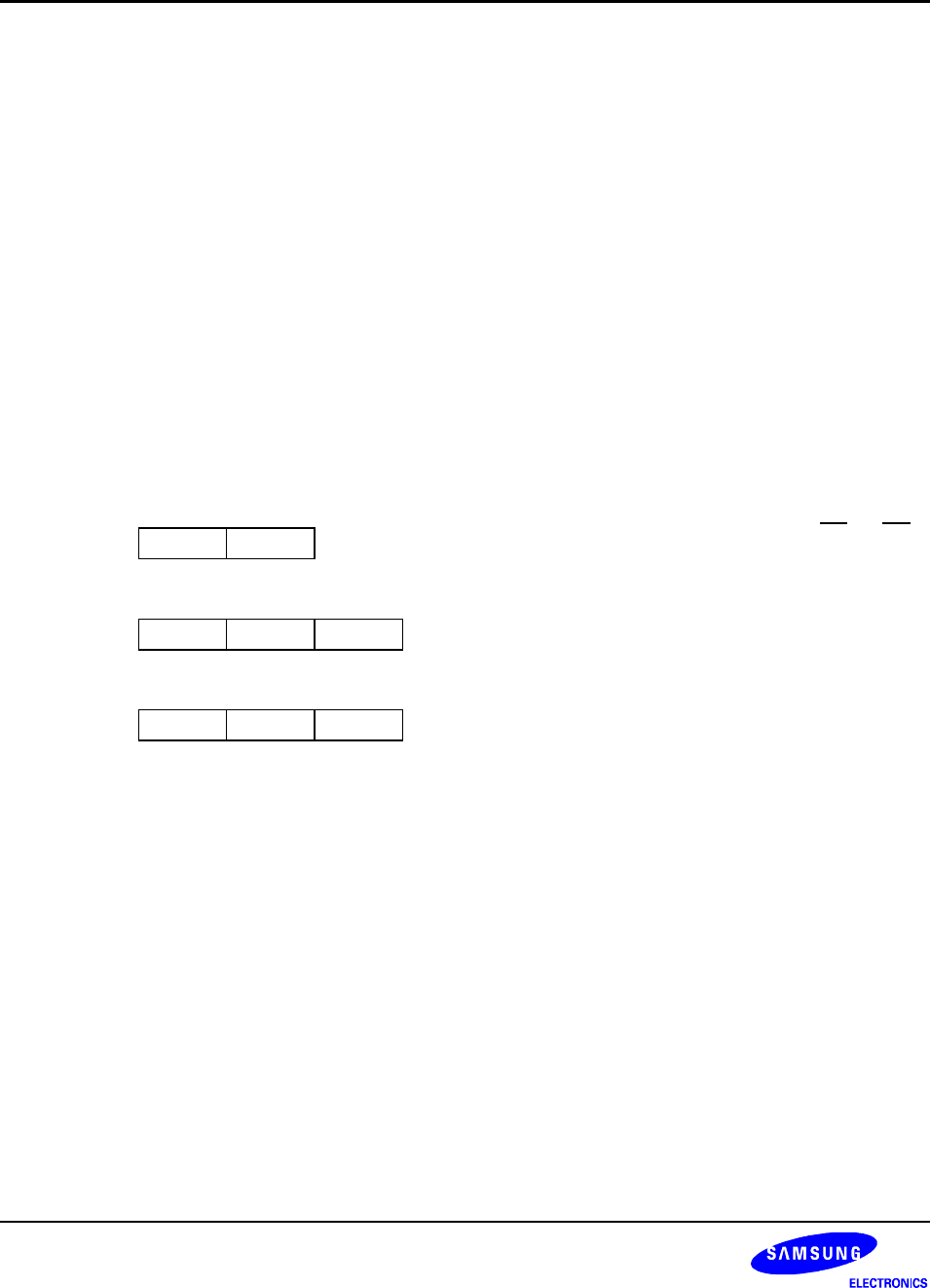

Format:

Bytes Cycles Opcode

(Hex)

Addr Mode

dst

src

opc dst | src

2 4 62 r r

6 63 r lr

opc src dst

3 6 64 R R

6 65 R IR

opc dst src

3 6 66 R IM

Examples: Given: R0 = 0C7H, R1 = 02H, R2 = 12H, register 00H = 2BH, register 01H = 02H, and

register 02H = 23H:

TCM R0,R1 → R0 = 0C7H, R1 = 02H, Z = "1"

TCM R0,@R1 → R0 = 0C7H, R1 = 02H, register 02H = 23H, Z = "0"

TCM 00H,01H → Register 00H = 2BH, register 01H = 02H, Z = "1"

TCM 00H,@01H → Register 00H = 2BH, register 01H = 02H,

register 02H = 23H, Z = "1"

TCM 00H,#34 → Register 00H = 2BH, Z = "0"

In the first example, if working register R0 contains the value 0C7H (11000111B) and register R1

the value 02H (00000010B), the statement "TCM R0,R1" tests bit one in the destination register

for a "1" value. Because the mask value corresponds to the test bit, the Z flag is set to logic one

and can be tested to determine the result of the TCM operation.