S3F80JB TIMER 2

13-5

TIMER 2 CONTROL REGISTER (T2CON)

The timer 2 control register, T2CON, is located in address E8H, Bank1, Set 1 and is read/write addressable.

T2CON contains control settings for the following T2 functions:

— Timer 2 input clock selection

— Timer 2 operating mode selection

— Timer 2 16-bit down counter clear

— Timer 2 overflow interrupt enable/disable

— Timer 2 match or capture interrupt enable/disable

— Timer 2 interrupt pending control (read for status, write to clear)

A reset operation clears T2CON to ‘00H’, selecting fosc divided by 4 as the T2 clock, configuring timer 2 as a

normal interval timer, and disabling the timer 2 interrupts.

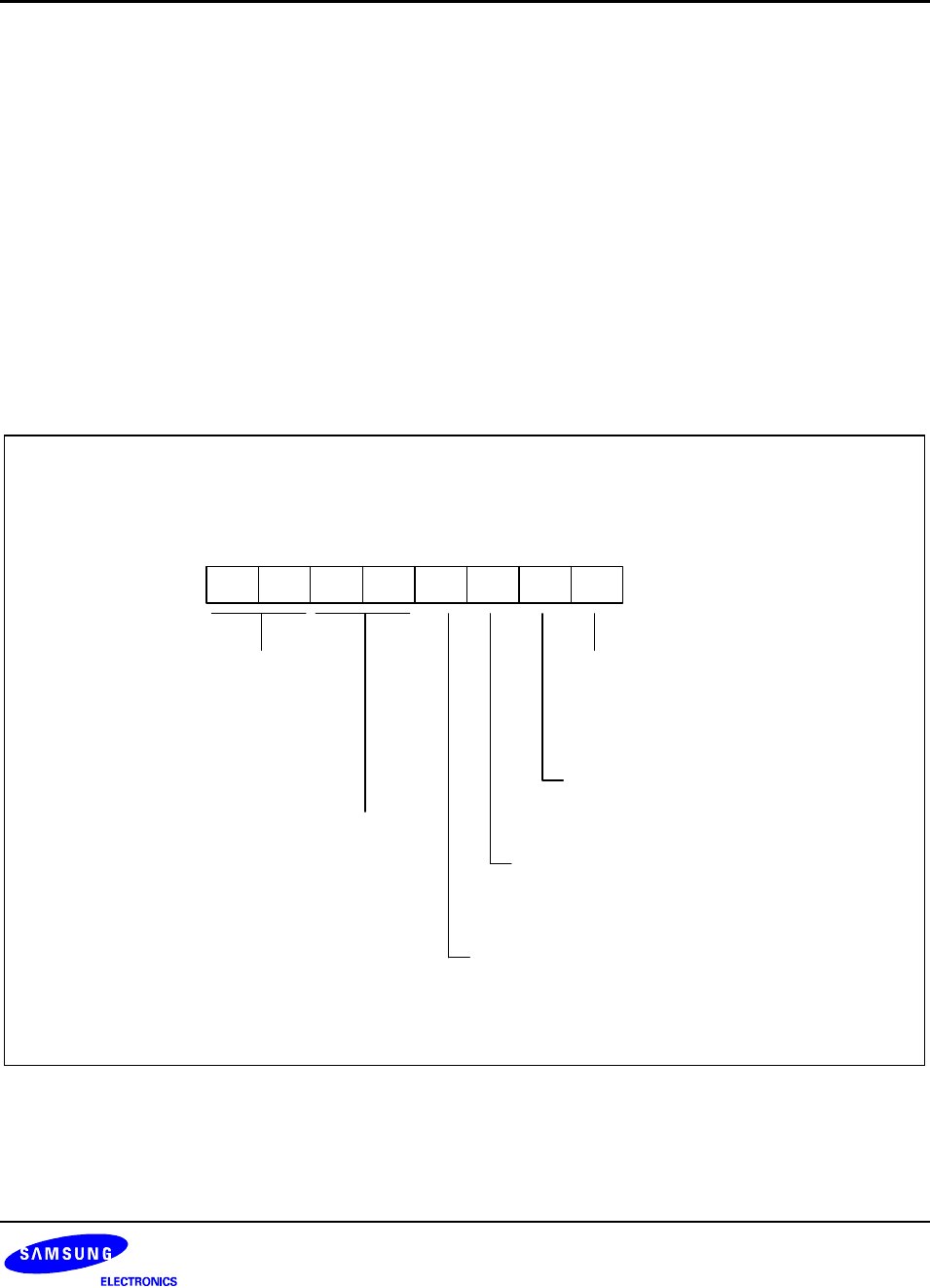

Timer 2 Control Register (T2CON)

E8H, Set 1, Bank 1, R/W

.7 .6 .5 .4 .3 .2 .1 .0MSB LSB

Timer 2 Interrupt Pending Bit:

0 = No interrupt pending

0 = Clear pending bit (when write)

1 = Interrupt is pending

Timer 2 Interrupt Match/capture Enable Bit:

0 = Disable interrupt

1 = Enable interrupt

Timer 2 Overflow Interrupt Enable Bit:

0 = Disable overflow interrupt

1 = Enable overflow interrupt

Timer 2 Input Clock Selection Bits:

00 = f

OSC

/4

01 = f

OSC

/8

10 = f

OSC

/16

11 = Internal clock (T-F/F)

Timer 2 Counter Clear Bit:

0 = No effect

1 = Clear the timer 0 counter (when write)

Timer 2 Operating Mode Selection Bits:

00 = Interval mode

01 = Capture mode (capture on rising edge,

counter running, OVF can occur)

10 = Capture mode (capture on falling edge,

counter running, OVF can occur)

11 = Capture mode (capture on rising and

falling edge, counter running, OVF can occur)

Figure 13-4. Timer 2 Control Register (T2CON)