RESET S3F80JB

8-18

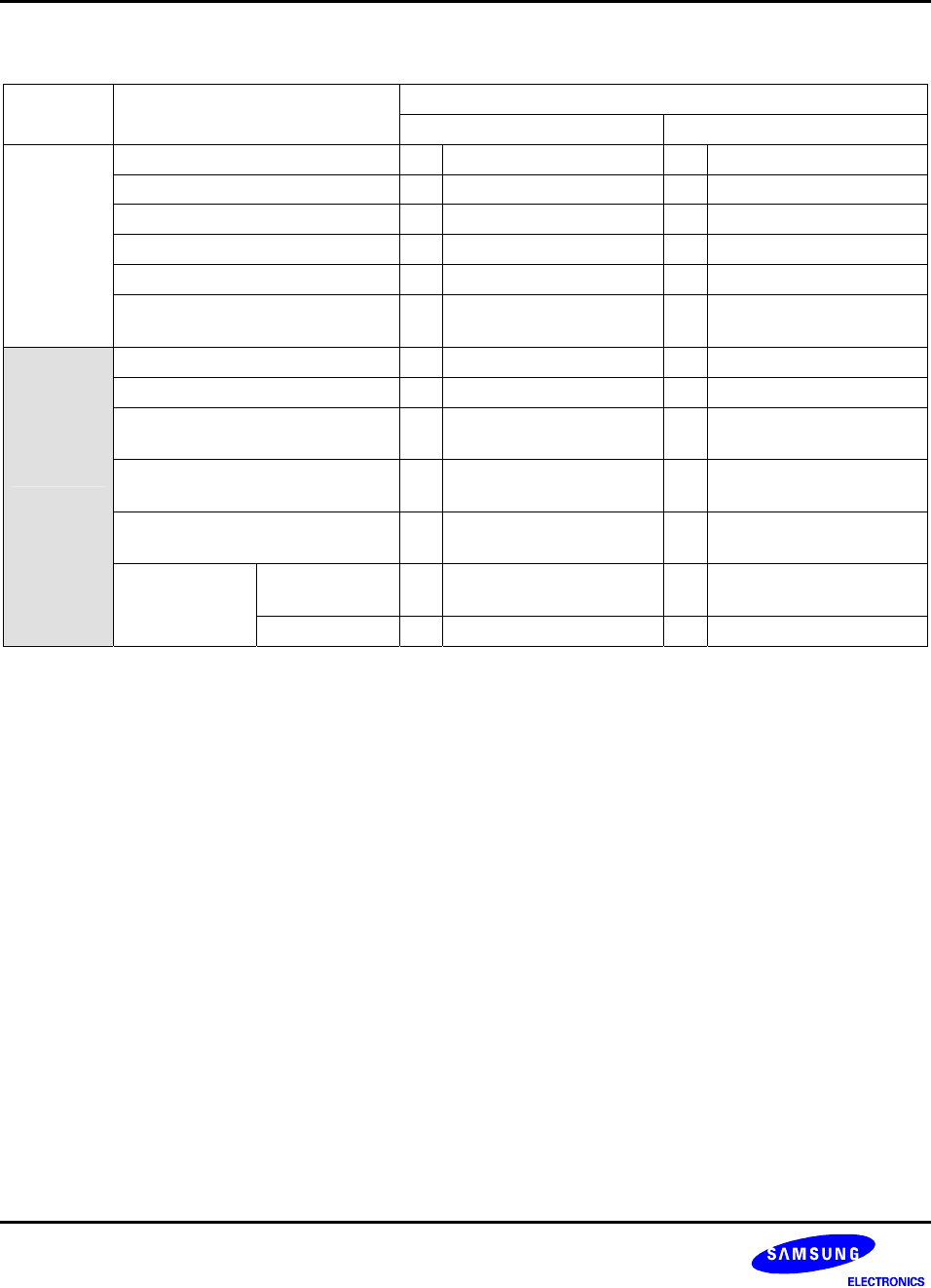

Table 8-5. Reset Generation According to the Condition of Smart Option

Smart option7th bit @3FH

Mode Reset Source

1 0

Reset Pin O Reset O Reset

Watch Dog Timer Enable O Reset O Reset

IPOR X Continue X Continue

LVD O Reset O Reset

External Interrupt (EI) P0 and P2 X External ISR X External ISR

Normal

Operating

External Interrupt (DI) P0 and

P2

X Continue X Continue

Reset Pin O Reset O Reset

Watch Dog Timer Enable X STOP X STOP

IPOR X STOP O STOP Release and

Reset

LVD O STOP Release and

Reset

X STOP

External Interrupt (EI-Enable) P0

and P2

X STOP Release and

External ISR

O STOP Release and

Reset

P0 & P2.4-2.7 X STOP Release and

Continue

O STOP Release and

Reset

Stop

Mode

SED&R

P2.0-2.3 X STOP X STOP

NOTES

1. ’X’ means that a corresponding reset source don’t generate reset signal. ‘O’ means that a

corresponding reset source generates reset signal.

2. ’Reset’ means that reset signal is generated and chip reset occurs,

3. ’Continue’ means that it executes the next instruction continuously without ISR execution.

4. ’External ISR’ means that chip executes the interrupt service routine of generated external interrupt

source.

5. ’STOP ‘ means that the chip is in stop state.

6. ‘STOP Release and External ISR’ means that chip executes the external interrupt service routine of

generated external interrupt source after STOP released.

7. ‘STOP Release and Continue’ means that executes the next instruction continuously after STOP

released.