110 Programmer’s Reference Manual

Intel® High Definition Audio BIOS Considerations

4.1.1 Intel

®

High Definition Audio/AC’ 97 Codec Detection

Before PCI device enumeration during POST, BIOS must determine the type of codec present on

the platform, then program the AZ/AC97# bit to select either Intel® HD Audio or AC’ 97 signal

mode, and program the corresponding bit in the Function Disable register (RCBA+ 3418h[6:4]) to

disable the other controller.

If the BIOS has inherent knowledge of which type of Codec(s) will be connected to the ICH7’s

signals, it can set the AZ/AC97# bit accordingly.

ICH7 also provides a mechanism for software to detect the type of the codec present on the

platform. Below is the Intel® HD Audio register used in the codec detection.

D27:F0:Reg40h – AZCTL—Intel® HD Audio Control

In the Intel® HD Audio environment the ICH7 drives BITCLK signal. The AZ/AC97# bit defaults

to 0 (AC97 mode) after reset, so the BITCLK signal will be configured as an input. The ICH7

samples the BITCLK signal. If it is toggling the CLKDET# bit will be set to 0. The BIOS can read

this bit and set the AZ/AC97# bit accordingly.

BIOS should perform this detection prior to PCI enumeration. The following is the BIOS software

flow for codec detection:

1. Ensure that ICH7 RCBA base address register (D31:F0:Reg F0h) is initialized and enabled.

2. Ensure that both AC’97 and Intel® HD Audio functions are present (RCBA+

3418[6:4]=000b), which is the power on default.

3. Set IOSE bit (D30:F2:Reg41h[0]=1), program the AC'97 function's PCI BARs with temporary

address values and enable IO BAR space via PCI command register.

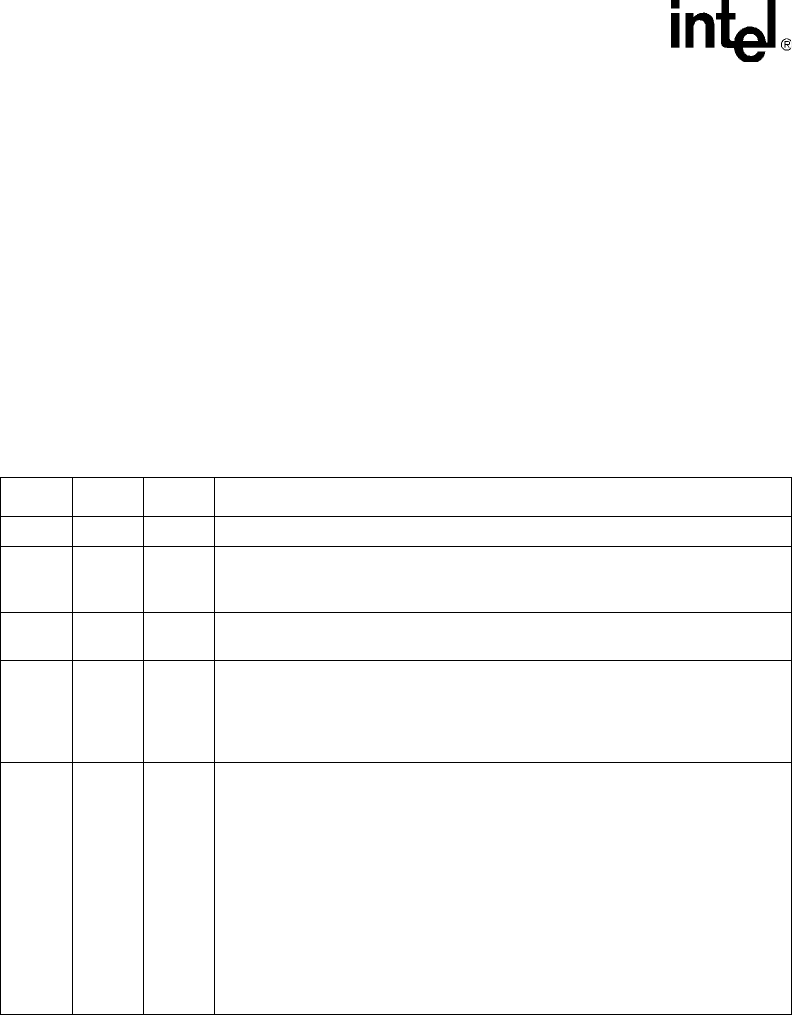

Bit Type Reset Description

7:4 RsvdP 0s Reserved

3R/W0

BITCLK Detect Clear (CLKDETCLR): Writing a 1 to this bit clears the

CLKDET# bit. The CLKDET# bit remains clear while this bit is set to 1. When a

0 is written to this bit, the clock detect circuit is operational and may be enabled.

2R/W0

BITCLK Detect Enable (CLKDETEN): Writing a 1 to this bit enables the clock

detection circuit. Writing a 0 latches the current state of the CLKDET# bit.

1RO0

BITCLK Detected Inverted (CLKDET#): This bit is modified by hardware. It is

set to 0 when the ICH7 detects that the BITCLK signal is toggling, indicating the

presence of an AC’97 codec on the link. Note that the CLKDETEN and

CLKDETCLR bits control the operation of this bit and must be manipulated

correctly to get a valid CLKDET# indicator.

0R/W0

Intel® HD Audio/AC97# Signal Mode (AZ/AC97#): This bit selects the mode

of the shared Intel® HD Audio/AC97 signals.

0 = AC97 mode is selected.

1 = Intel® HD Audio mode is selected.

The bit defaults to 0 (AC97 mode) to protect against contention on BCLK when

an AC97 codec is connected.

Note that this bit has no effect on the visibility of the AC97 and Intel® HD Audio

function configuration space. That is controlled through individual function

enable bits.

This bit is in the resume well and only cleared on a power-on reset. Software

must not make assumptions about the reset state of this bit and must set it

appropriately.