36 Programmer’s Reference Manual

Intel

®

High Definition Audio Controller Registers (D27:F0)

1.2 Intel

®

High Definition Audio Memory Mapped

Configuration Registers

(

Intel

®

High Definition Audio— D27:F0)

The base memory location for these memory mapped configuration registers is specified in the

HDBAR register (D27:F0:offset 10h and D27:F0:offset 14h). The individual registers are then

accessible at HDBAR + Offset as indicated in Table 1-2.

These memory mapped registers must be accessed in byte, word, or DWord quantities.

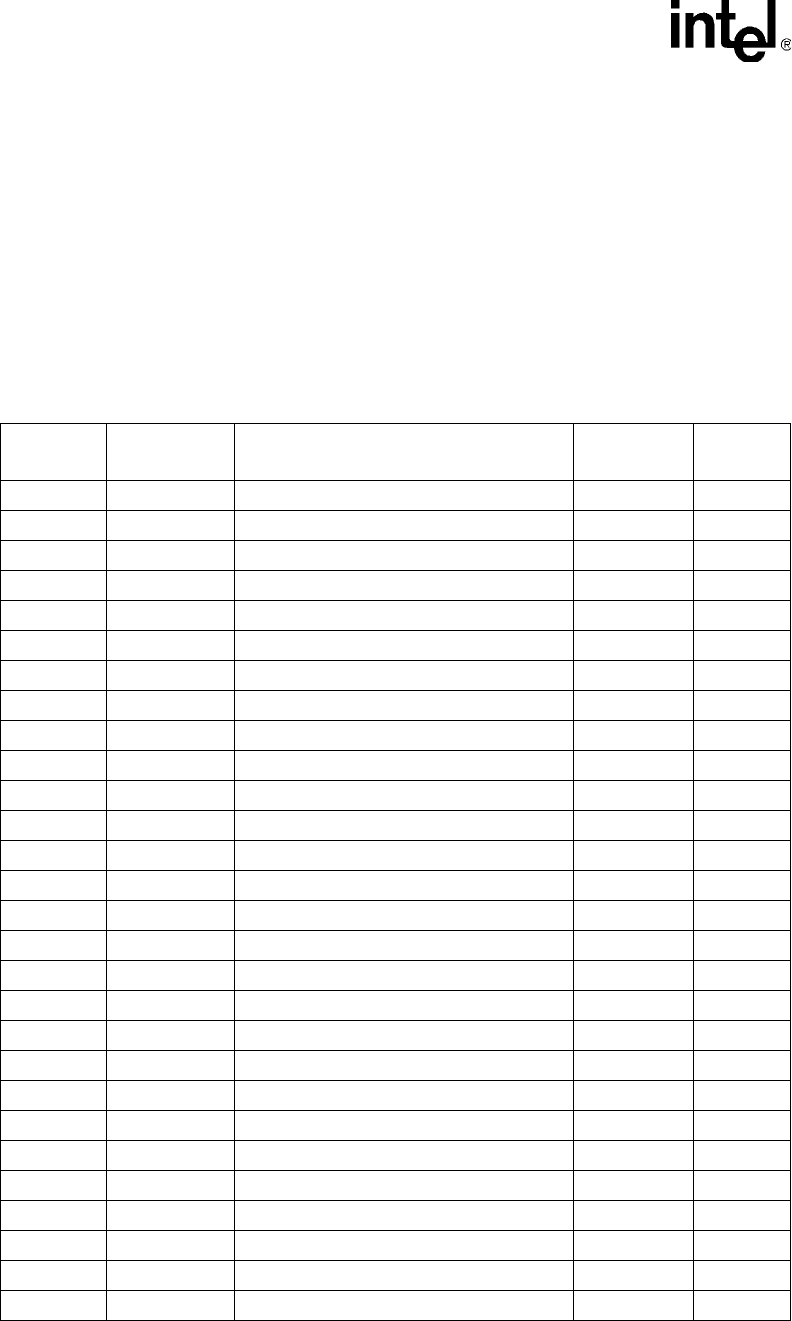

Table 1-2. Intel

®

High Definition Audio PCI Register Address Map

(Intel

®

High Definition Audio D27:F0) (Sheet 1 of 4)

HDBAR +

Offset

Mnemonic Register Name Default Access

00h–01h GCAP Global Capabilities 4401h RO

02h VMIN Minor Version 00h RO

03h VMAJ Major Version 01h RO

04h–05h OUTPAY Output Payload Capability 003Ch RO

06h–07h INPAY Input Payload Capability 001Dh RO

08h–0Bh GCTL Global Control 00000000h R/W

0Ch–0Dh WAKEEN Wake Enable 0000h R/W

0Eh–0Fh STATESTS State Change Status 0000h R/WC

10h–11h GSTS Global Status 0000h R/WC

12h–13h Rsv Reserved 0000h RO

18h–19h OUTSTRMPAY Output Stream Payload Capability 0030h RO

1Ah–1Bh INSTRMPAY Input Stream Payload Capability 0018h RO

1Ch–1Fh Rsv Reserved 00000000h RO

20h–23h INTCTL Interrupt Control 00000000h R/W

24h–27h INTSTS Interrupt Status 00000000h RO

30h–33h WALCLK Wall Clock Counter 00000000h RO

34h–37h SSYNC Stream Synchronization 00000000h R/W

40h–43h CORBLBASE CORB Lower Base Address 00000000h R/W, RO

44h–47h CORBUBASE CORB Upper Base Address 00000000h R/W

48h–49h CORBWP CORB Write Pointer 0000h R/W

4Ah–4Bh CORBRP CORB Read Pointer 0000h R/W

4Ch CORBCTL CORB Control 00h R/W

4Dh CORBST CORB Status 00h R/WC

4Eh CORBSIZE CORB Size 42h RO

50h–53h RIRBLBASE RIRB Lower Base Address 00000000h R/W, RO

54h–57h RIRBUBASE RIRB Upper Base Address 00000000h R/W

58h–59h RIRBWP RIRB Write Pointer 0000h R/W, RO

5Ah–5Bh RINTCNT Response Interrupt Count 0000h R/W