Programmer’s Reference Manual 39

Intel

®

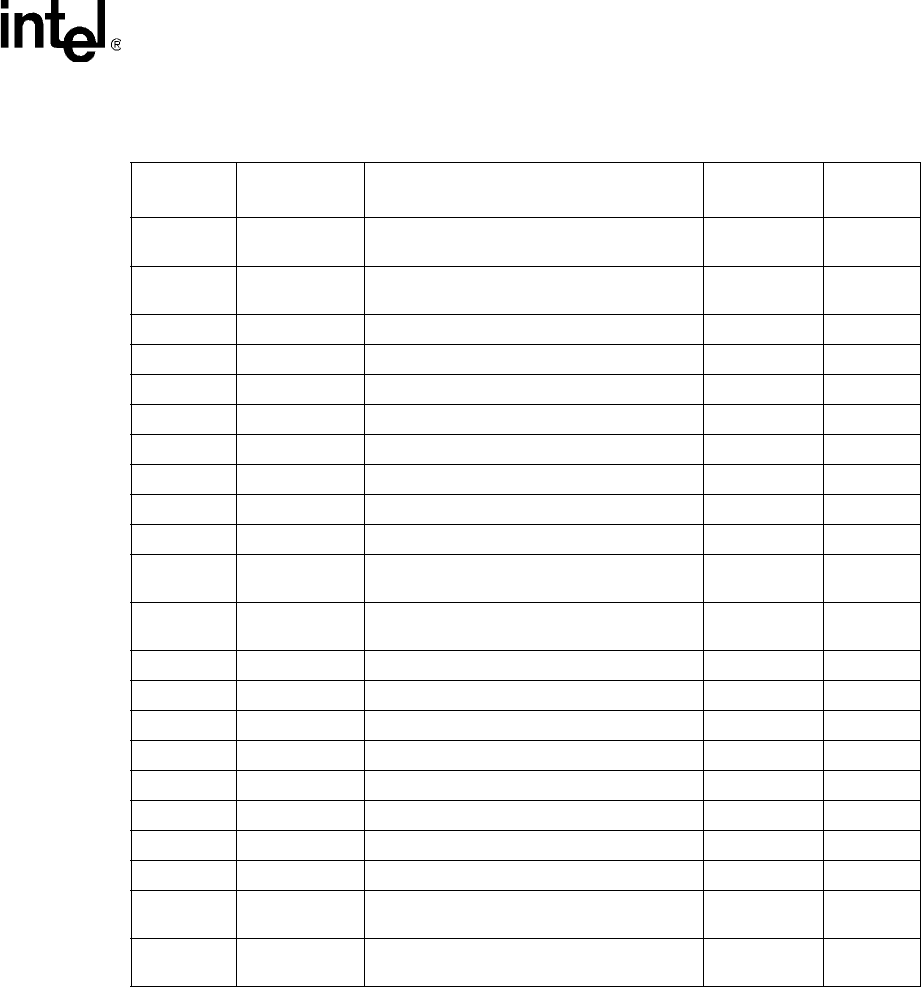

High Definition Audio Controller Registers (D27:F0)

138h–13Bh OSD1BDPL

OSD1 Buffer Descriptor List Pointer-Lower

Base Address

00000000h R/W, RO

13Ch–13Fh OSD1BDPU

OSD1 Buffer Description List Pointer-Upper

Base Address

00000000h R/W

140h–142h OSD2CTL Output Stream Descriptor 2 (OSD2) Control 040000h R/W, RO

143h OSD2STS OSD2 Status 00h R/WC, RO

144h–147h OSD2LPIB OSD2 Link Position in Buffer 00000000h RO

148h–14Bh OSD2CBL OSD2 Cyclic Buffer Length 00000000h R/W

14Ch–14Dh OSD2LVI OSD2 Last Valid Index 0000h R/W

14Eh–14Fh OSD2FIFOW OSD2 FIFO Watermark 0004h R/W

150h–151h OSD2FIFOS OSD2 FIFO Size 00BFh R/W

152h–153h OSD2FMT OSD2 Format 0000h R/W

158h–15Bh OSD2BDPL

OSD2 Buffer Descriptor List Pointer-Lower

Base Address

00000000h R/W, RO

15Ch–15Fh OSD2BDPU

OSD2 Buffer Description List Pointer-Upper

Base Address

00000000h R/W

160h–162h OSD3CTL Output Stream Descriptor 3 (OSD3) Control 040000h R/W, RO

163h OSD3STS OSD3 Status 00h R/WC, RO

164h–167h OSD3LPIB OSD3 Link Position in Buffer 00000000h RO

168h–16Bh OSD3CBL OSD3 Cyclic Buffer Length 00000000h R/W

16Ch–16Dh OSD3LVI OSD3 Last Valid Index 0000h R/W

16Eh–16Fh OSD3FIFOW OSD3 FIFO Watermark 0004h R/W

170h–171h OSD3FIFOS OSD3 FIFO Size 00BFh R/W

172h–173h OSD3FMT OSD3 Format 0000h R/W

178h–17Bh OSD3BDPL

OSD3 Buffer Descriptor List Pointer-Lower

Base Address

00000000h R/W, RO

17Ch–17Fh OSD3BDPU

OSD3 Buffer Description List Pointer-Upper

Base Address

00000000h R/W

Table 1-2. Intel

®

High Definition Audio PCI Register Address Map

(Intel

®

High Definition Audio D27:F0) (Sheet 4 of 4)

HDBAR +

Offset

Mnemonic Register Name Default Access