Programmer’s Reference Manual 53

Intel

®

High Definition Audio Controller Registers (D27:F0)

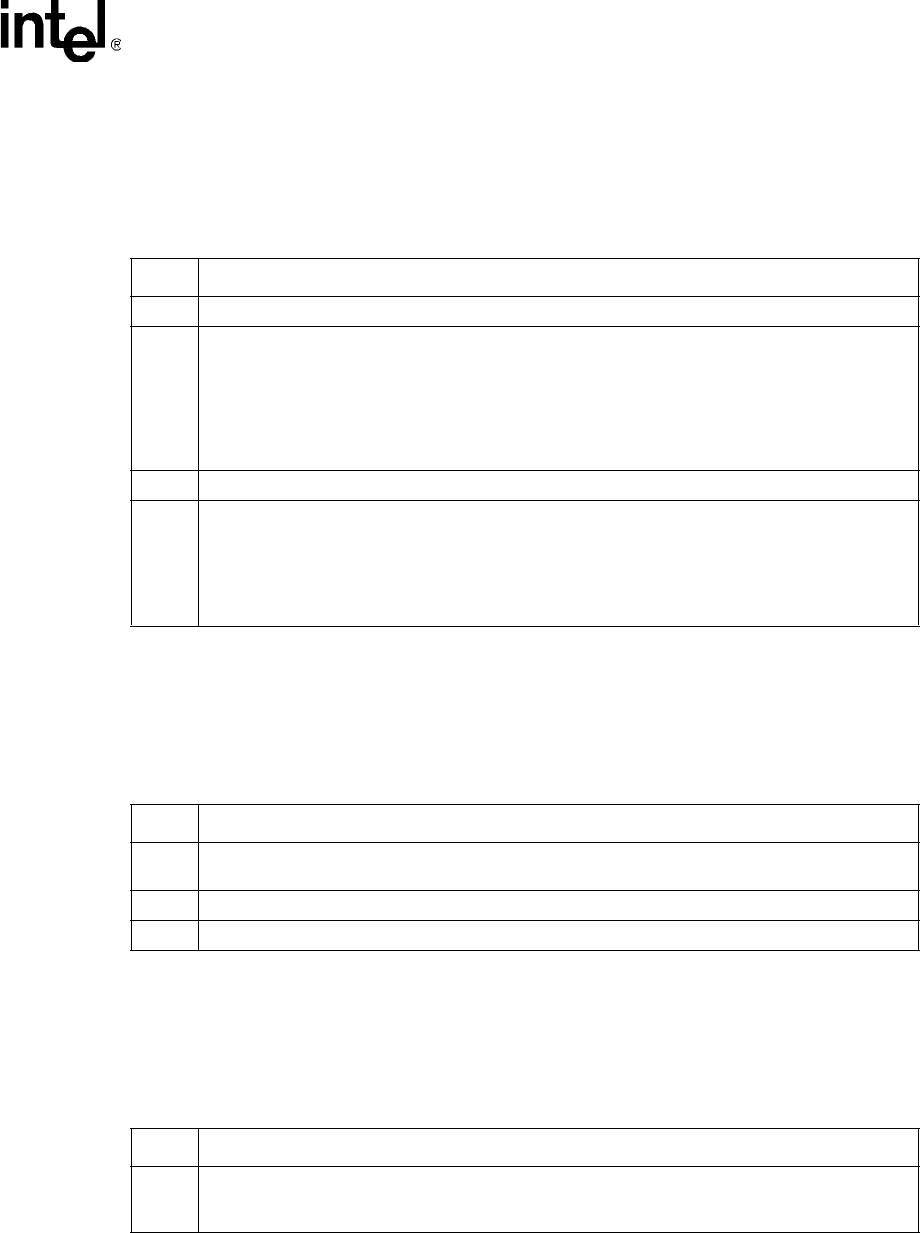

1.2.28 RIRBSTS—RIRB Status Register

(Intel

®

High Definition Audio Controller—D27:F0)

Memory Address: HDBAR + 5Dh Attribute: R/WC

Default Value: 00h Size: 8 bits

1.2.29 RIRBSIZE—RIRB Size Register

(Intel

®

High Definition Audio Controller—D27:F0)

Memory Address: HDBAR + 5Eh Attribute: RO

Default Value: 42h Size: 8 bits

1.2.30 IC—Immediate Command Register

(Intel

®

High Definition Audio Controller—D27:F0)

Memory Address: HDBAR + 60h Attribute: R/W

Default Value: 00000000h Size: 32 bits

Bit Description

7:3 Reserved.

2

Response Overrun Interrupt Status — R/WC.

0 = Software clears this bit by writing a 1 to it.

1 = Software sets this bit to 1 when the RIRB DMA engine is not able to write the incoming

responses to memory before additional incoming responses overrun the internal FIFO. When

the overrun occurs, the hardware will drop the responses that overrun the buffer. An interrupt

may be generated if the Response Overrun Interrupt Control bit is set. Note that this status bit is

set even if an interrupt is not enabled for this event.

1 Reserved.

0

Response Interrupt — R/WC.

0 = Software clears this bit by writing a 1 to it.

1 = Hardware sets this bit to 1 when an interrupt has been generated after N number of Responses

are sent to the RIRB buffer OR when an empty Response slot is encountered on all SDI[x]

inputs (whichever occurs first). Note that this status bit is set even if an interrupt is not enabled

for this event.

Bit Description

7:4

RIRB Size Capability — RO. Hardwired to 0100b indicating that the ICH7 only supports a RIRB size

of 256 RIRB entries (2048B)

3:2 Reserved.

1:0 RIRB Size — RO. Hardwired to 10b which sets the CORB size to 256 entries (2048B)

Bit Description

31:0

Immediate Command Write — R/W. The command to be sent to the codec via the Immediate

Command mechanism is written to this register. The command stored in this register is sent out over

the link during the next available frame after a 1 is written to the ICB bit (HDBAR + 68h: bit 0)