66 Programmer’s Reference Manual

AC ’97 Audio Controller Registers (D30:F2)

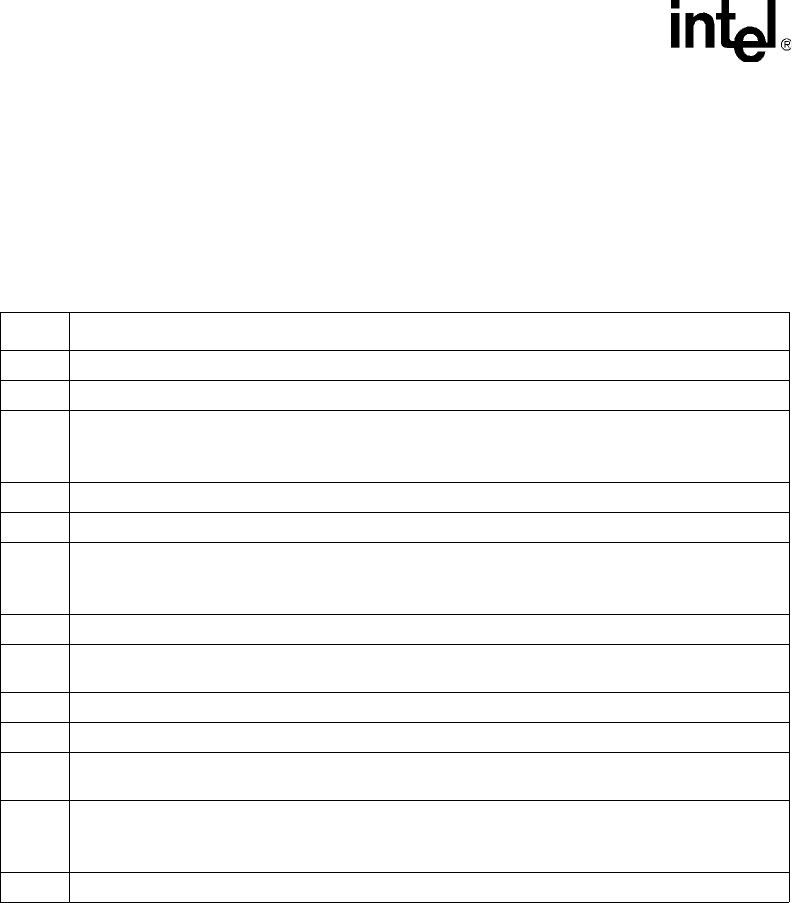

2.1.4 PCISTS—PCI Status Register (Audio—D30:F2)

Offset: 06h–07h Attribute: RO, R/WC

Default Value 0280h Size: 16 bits

Lockable: No Power Well: Core

PCISTA is a 16-bit status register. Refer to the PCI 2.3 specification for complete details on each

bit.

Bit Description

15 Detected Parity Error (DPE). Not implemented. Hardwired to 0.

14 Signaled System Error (SSE) — RO. Not implemented. Hardwired to 0.

13

Master Abort Status (MAS) — R/WC. Software clears this bit by writing a 1 to it.

0 = No master abort generated.

1 = Bus Master AC '97 2.3 interface function, as a master, generates a master abort.

12 Reserved — RO. Will always read as 0.

11 Signaled Target Abort (STA) — RO. Not implemented. Hardwired to 0.

10:9

DEVSEL# Timing Status (DEV_STS) — RO. This 2-bit field reflects the ICH7's DEVSEL# timing

when performing a positive decode.

01b = Medium timing.

8 Data Parity Error Detected (DPED) — RO. Not implemented. Hardwired to 0.

7

Fast Back to Back Capable (FB2BC) — RO. Hardwired to 1. This bit indicates that the ICH7 as a

target is capable of fast back-to-back transactions.

6 UDF Supported — RO. Not implemented. Hardwired to 0.

5 66 MHz Capable (66MHZ_CAP) — RO. Hardwired to 0.

4

Capabilities List (CAP_LIST) — RO. Indicates that the controller contains a capabilities pointer list.

The first item is pointed to by looking at configuration offset 34h.

3

Interrupt Status (IS) — RO.

0 = This bit is 0 after the interrupt is cleared.

1 = This bit is 1 when the INTx# is asserted.

2:0 Reserved.