Programmer’s Reference Manual 65

AC ’97 Audio Controller Registers (D30:F2)

2.1.3 PCICMD—PCI Command Register (Audio—D30:F2)

Address Offset: 04h–05h Attribute: R/W, RO

Default Value: 0000h Size: 16 bits

Lockable: No Power Well: Core

PCICMD is a 16-bit control register. Refer to the PCI 2.3 specification for complete details on each

bit.

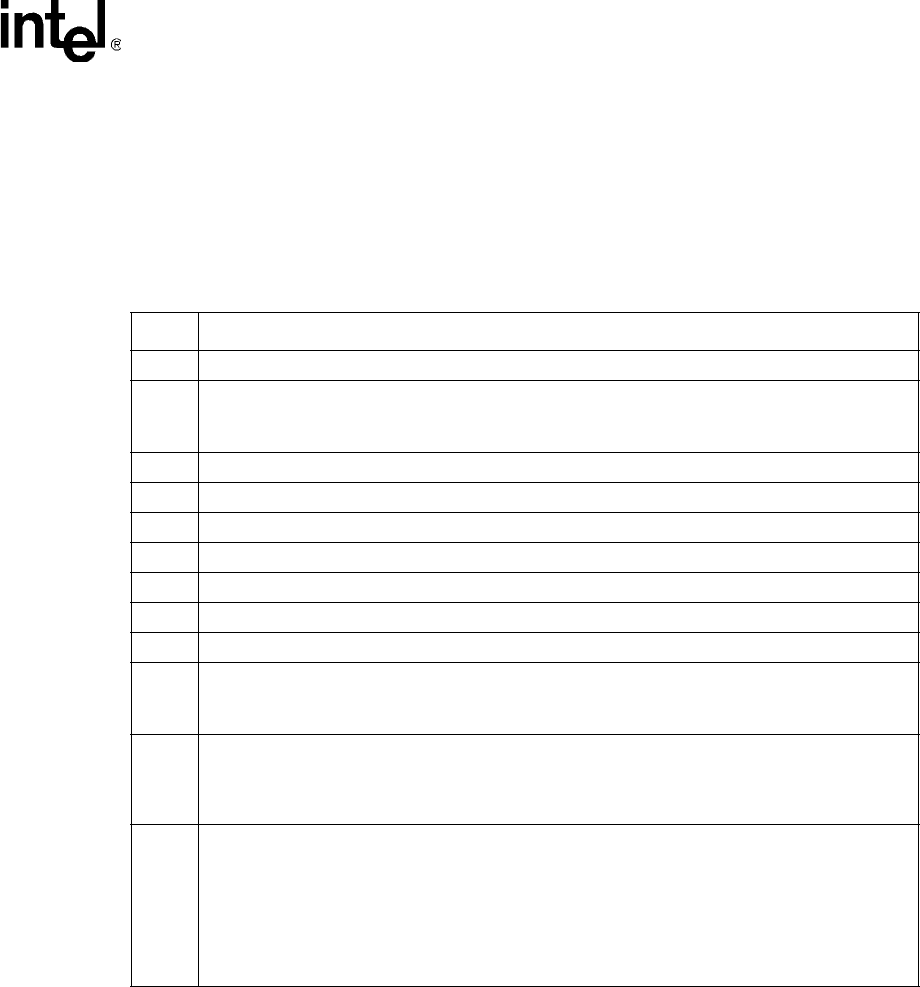

Bit Description

15:11 Reserved. Read 0.

10

Interrupt Disable (ID) — R/W.

0 = The INTx# signals may be asserted and MSIs may be generated.

1 = The AC ‘97 controller’s INTx# signal will be de-asserted and it may not generate MSIs.

9 Fast Back to Back Enable (FBE) — RO. Not implemented. Hardwired to 0.

8 SERR# Enable (SERR_EN) — RO. Not implemented. Hardwired to 0.

7 Wait Cycle Control (WCC) — RO. Not implemented. Hardwired to 0.

6 Parity Error Response (PER) — RO. Not implemented. Hardwired to 0.

5 VGA Palette Snoop (VPS). Not implemented. Hardwired to 0.

4 Memory Write and Invalidate Enable (MWIE) — RO. Not implemented. Hardwired to 0.

3 Special Cycle Enable (SCE). Not implemented. Hardwired to 0.

2

Bus Master Enable (BME) — R/W. Controls standard PCI bus mastering capabilities.

0 = Disable

1 = Enable

1

Memory Space Enable (MSE) — R/W. Enables memory space addresses to the AC ’97 Audio

controller.

0 = Disable

1 = Enable

0

I/O Space Enable (IOSE) — R/W. This bit controls access to the AC ’97 Audio controller I/O space

registers.

0 = Disable (Default).

1 = Enable access to I/O space. The Native PCI Mode Base Address register should be

programmed prior to setting this bit.

NOTE: This bit becomes writable when the IOSE bit in offset 41h is set. If at any point software

decides to clear the IOSE bit, software must first clear the IOS bit.