90 Programmer’s Reference Manual

AC ’97 Modem Controller Registers (D30:F3)

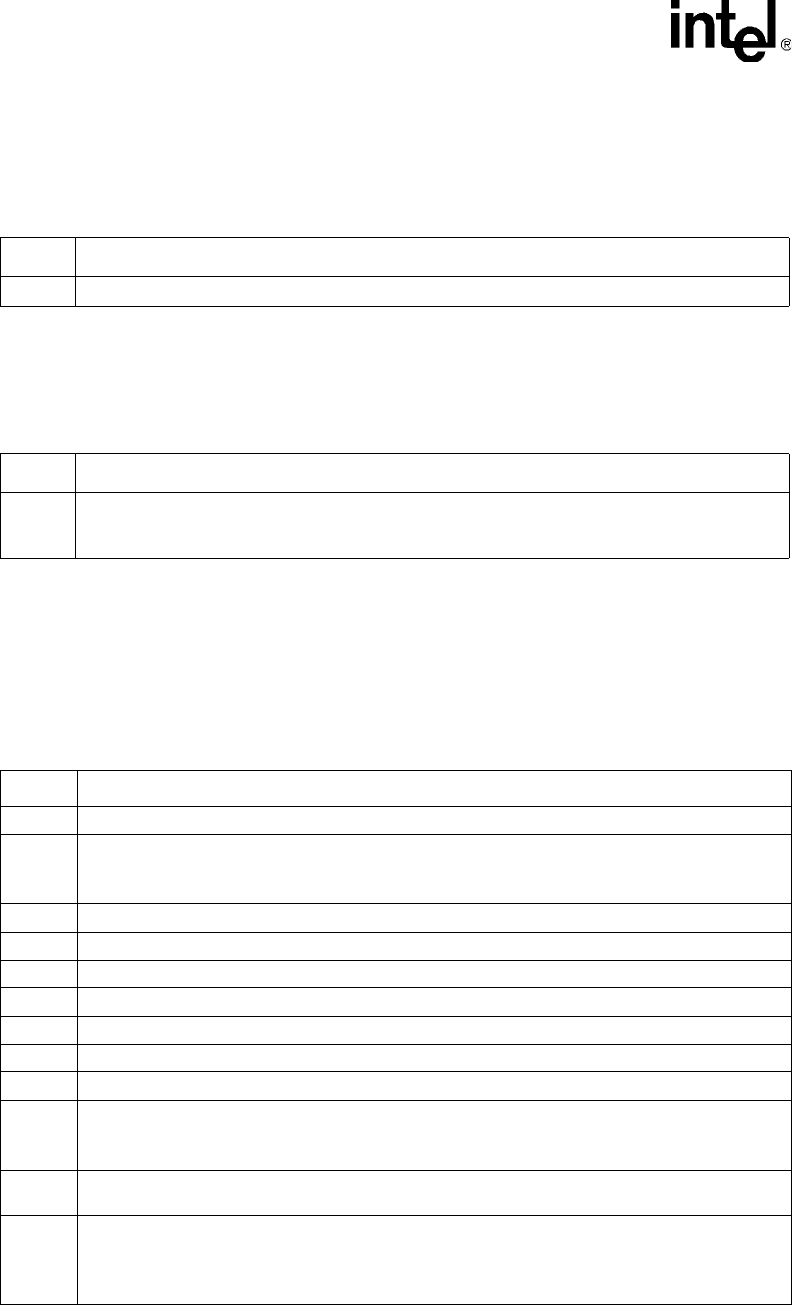

3.1.1 VID—Vendor Identification Register (Modem—D30:F3)

Address Offset: 00h–01h Attribute: RO

Default Value: 8086 Size: 16 Bits

Lockable: No Power Well: Core

3.1.2 DID—Device Identification Register (Modem—D30:F3)

Address Offset: 02h–03h Attribute: RO

Default Value: See bit description Size: 16 Bits

Lockable: No Power Well: Core

3.1.3 PCICMD—PCI Command Register (Modem—D30:F3)

Address Offset: 04h–05h Attribute: R/W, RO

Default Value: 0000h Size: 16 bits

Lockable: No Power Well: Core

PCICMD is a 16-bit control register. Refer to the PCI Local Bus Specification for complete details

on each bit.

Bit Description

15:0 Vendor ID — RO. This is a 16-bit value assigned to Intel.

Bit Description

15:0

Device ID — RO. This is a 16-bit value assigned to the Intel

®

ICH7 AC ‘97 Modem controller. Refer

to the Intel

®

I/O Controller Hub 7 (ICH7) Family Specification Update for the value of the Device ID

Register.

Bit Description

15:11 Reserved. Read 0.

10

Interrupt Disable (ID)— R/W.

0 = The INTx# signals may be asserted and MSIs may be generated.

1 = The AC ‘97 controller’s INTx# signal will be de-asserted and it may not generate MSIs.

9 Fast Back to Back Enable (FBE) — RO. Not implemented. Hardwired to 0.

8 SERR# Enable (SERR_EN) — RO. Not implemented. Hardwired to 0.

7 Wait Cycle Control (WCC) — RO. Not implemented. Hardwired to 0.

6 Parity Error Response (PER) — RO. Not implemented. Hardwired to 0.

5 VGA Palette Snoop (VPS) — RO. Not implemented. Hardwired to 0.

4 Memory Write and Invalidate Enable (MWIE) — RO. Not implemented. Hardwired to 0.

3 Special Cycle Enable (SCE) — RO. Not implemented. Hardwired to 0.

2

Bus Master Enable (BME) — R/W. This bit controls standard PCI bus mastering capabilities.

0 = Disable

1 = Enable

1

Memory Space Enable (MSE) — RO. Hardwired to 0, AC ‘97 does not respond to memory

accesses.

0

I/O Space Enable (IOSE) — R/W. This bit controls access to the I/O space registers.

0 = Disable access. (default = 0).

1 = Enable access to I/O space. The Native PCI Mode Base Address register should be

programmed prior to setting this bit.