Programmer’s Reference Manual 89

AC ’97 Modem Controller Registers (D30:F3)

3 AC ’97 Modem Controller

Registers (D30:F3)

3.1 AC ’97 Modem PCI Configuration Space (D30:F3)

Note: Registers that are not shown should be treated as Reserved.

Note: Internal reset as a result of D3

HOT

to D0 transition will reset all the core well registers except the

following BIOS programmed registers as BIOS may not be invoked following the D3-to-D0

transition. All resume well registers will not be reset by the D3

HOT

to D0 transition.

Core well registers not reset by the D3

HOT

to D0 transition:

• offset 2Ch–2Dh – Subsystem Vendor ID (SVID)

• offset 2Eh–2Fh – Subsystem ID (SID)

Resume well registers will not be reset by the D3

HOT

to D0 transition:

• offset 54h–55h – Power Management Control and Status (PCS)

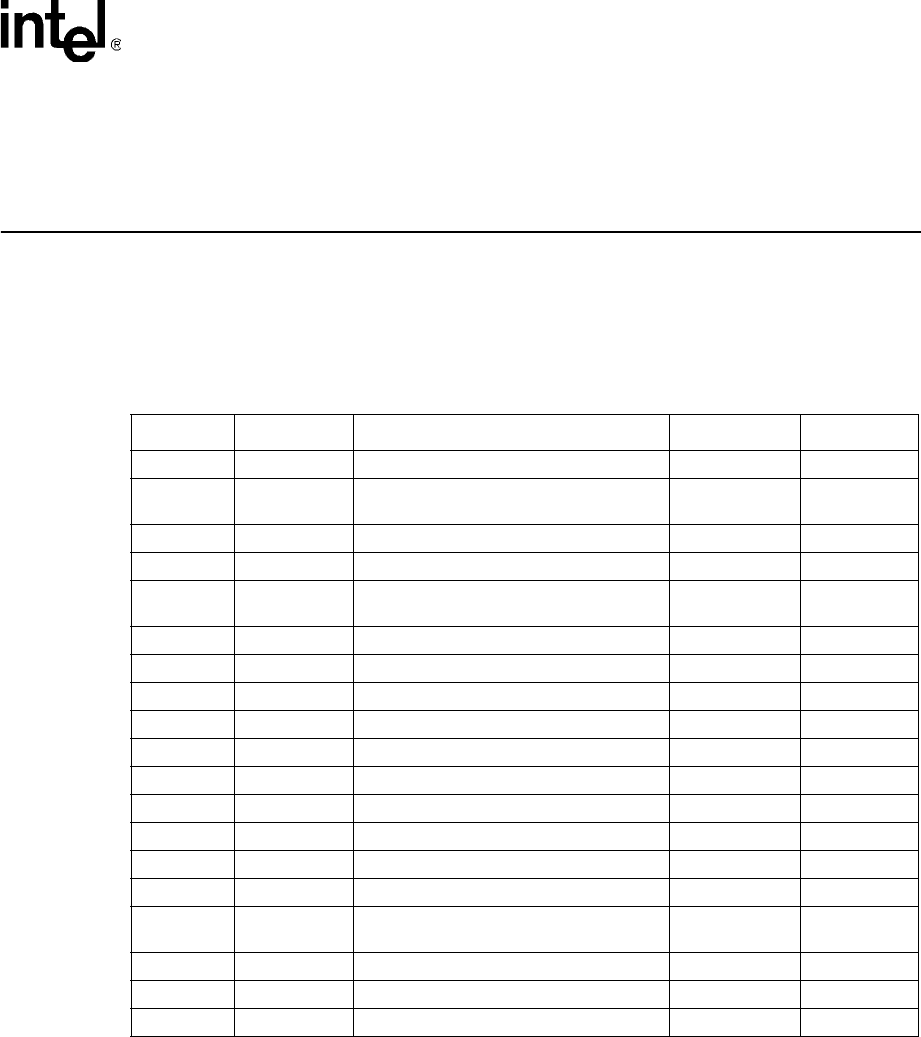

Table 3-1. AC ‘97 Modem PCI Register Address Map (Modem—D30:F3)

Offset Mnemonic Register Default Access

00h–01h VID Vendor Identification 8086 RO

02h–03h DID Device Identification

See register

description

RO

04h–05h PCICMD PCI Command 0000h R/W, RO

06h–07h PCISTS PCI Status 0290h R/WC, RO

08h RID Revision Identification

See register

description

RO

09h PI Programming Interface 00h RO

0Ah SCC Sub Class Code 03h RO

0Bh BCC Base Class Code 07h RO

0Eh HEADTYP Header Type 00h RO

10h–13h MMBAR Modem Mixer Base Address 00000001h R/W, RO

14h–17h MBAR Modem Base Address 00000001h R/W, RO

2Ch–2Dh SVID Subsystem Vendor Identification 0000h R/WO

2Eh–2Fh SID Subsystem Identification 0000h R/WO

34h CAP_PTR Capabilities Pointer 50h RO

3Ch INT_LN Interrupt Line 00h R/W

3Dh INT_PN Interrupt Pin

See register

description

RO

50h–51h PID PCI Power Management Capability ID 0001h RO

52h–53h PC Power Management Capabilities C9C2h RO

54h–55h PCS Power Management Control and Status 0000h R/W, R/WC