Programmer’s Reference Manual 57

Intel

®

High Definition Audio Controller Registers (D27:F0)

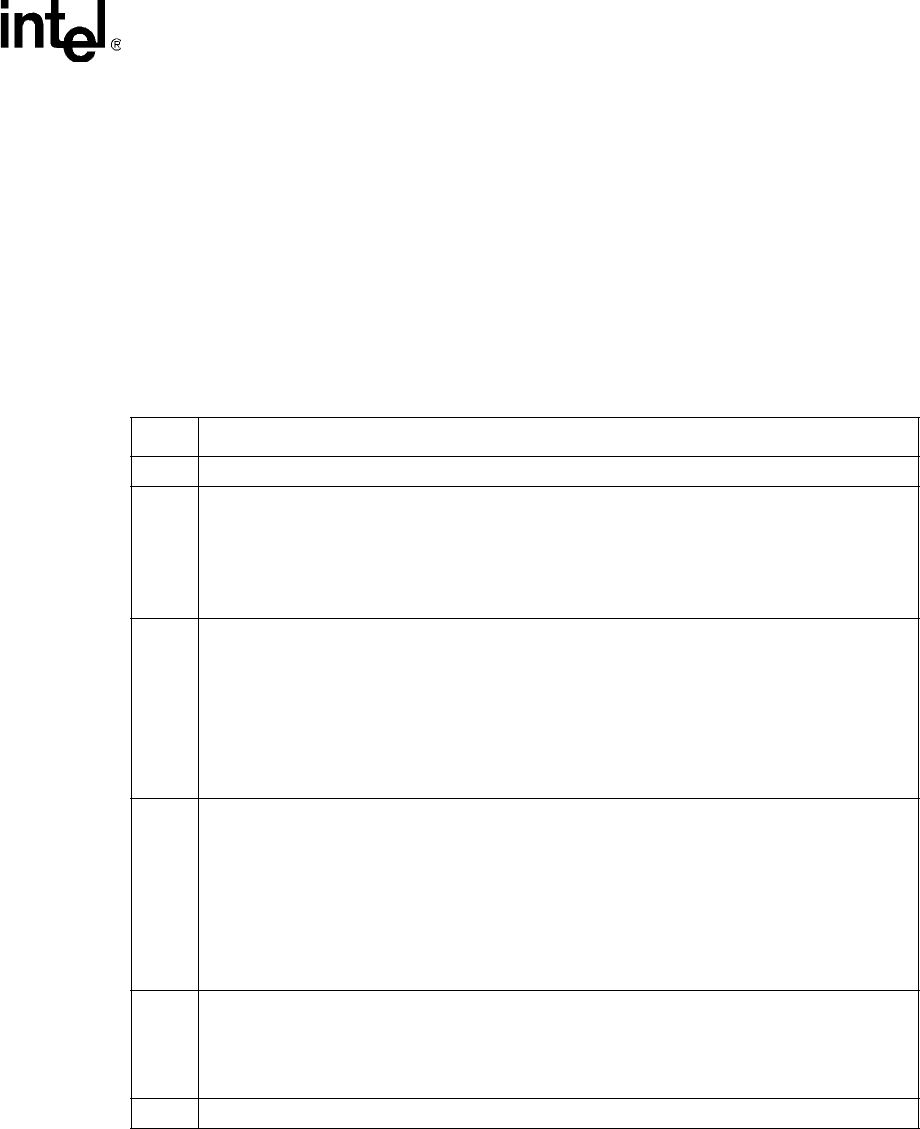

1.2.36 SDSTS—Stream Descriptor Status Register

(Intel

®

High Definition Audio Controller—D27:F0)

Memory Address: Input Stream[0]: HDBAR + 83h Attribute: R/WC, RO

Input Stream[1]: HDBAR + A3h

Input Stream[2]: HDBAR + C3h

Input Stream[3]: HDBAR + E3h

Output Stream[0]: HDBAR + 103h

Output Stream[1]: HDBAR + 123h

Output Stream[2]: HDBAR + 143h

Output Stream[3]: HDBAR + 163h

Default Value: 00h Size: 8 bits

Bit Description

7:6 Reserved.

5

FIFO Ready (FIFORDY) — RO.

For output streams, the controller hardware will set this bit to 1 while the output DMA FIFO contains

enough data to maintain the stream on the link. This bit defaults to 0 on reset because the FIFO is

cleared on a reset.

For input streams, the controller hardware will set this bit to 1 when a valid descriptor is loaded and

the engine is ready for the RUN bit to be set.

4

Descriptor Error — R/WC.

0 = No error detected.

1 = A serious error occurred during the fetch of a descriptor. This could be a result of a Master

Abort, a parity or ECC error on the bus, or any other error which renders the current Buffer

Descriptor or Buffer Descriptor list useless. This error is treated as a fatal stream error, as the

stream cannot continue running. The RUN bit will be cleared and the stream will stop.

NOTE: Software may attempt to restart the stream engine after addressing the cause of the error

and writing a 1 to this bit to clear it.

3

FIFO Error — R/WC. The bit is cleared by writing a 1 to it.

0 = No error detected.

1 = FIFO error occurred. This bit is set even if an interrupt is not enabled.

For an input stream, this indicates a FIFO overrun occurring while the RUN bit is set. When this

happens, the FIFO pointers do not increment and the incoming data is not written into the FIFO,

thereby being lost.

For an output stream, this indicates a FIFO underrun when there are still buffers to send. The

hardware should not transmit anything on the link for the associated stream if there is not valid data

to send.

2

Buffer Completion Interrupt Status — R/WC.

0 = Last sample of a buffer has Not been processed as described below.

1 = Set to 1 by the hardware after the last sample of a buffer has been processed, AND if the

Interrupt on Completion bit is set in the command byte of the buffer descriptor. It remains active

until software clears it by writing a 1 to it.

1:0 Reserved.