78 Programmer’s Reference Manual

AC ’97 Audio Controller Registers (D30:F2)

Note: Internal reset as a result of D3

HOT

to D0 transition will reset all the core well registers except the

registers shared with the AC ’97 Modem (GCR, GSR, CASR). All resume well registers will not be

reset by the D3

HOT

to D0 transition.

Core well registers and bits not reset by the D3

HOT

to D0 transition:

• offset 2Ch–2Fh – bits 6:0 Global Control (GLOB_CNT)

• offset 30h–33h – bits [29,15,11:10,0] Global Status (GLOB_STA)

• offset 34h – Codec Access Semaphore Register (CAS)

Resume well registers and bits will not be reset by the D3

HOT

to D0 transition:

• offset 30h–33h – bits [17:16] Global Status (GLOB_STA)

2.2.1 x_BDBAR—Buffer Descriptor Base Address Register

(Audio—D30:F2)

I/O Address: NABMBAR + 00h (PIBDBAR), Attribute: R/W

NABMBAR + 10h (POBDBAR),

NABMBAR + 20h (MCBDBAR)

MBBAR + 40h (MC2BDBAR)

MBBAR + 50h (PI2BDBAR)

MBBAR + 60h (SPBAR)

Default Value: 00000000h Size: 32 bits

Lockable: No Power Well: Core

Software can read the register at offset 00h by performing a single 32-bit read from address offset

00h. Reads across DWord boundaries are not supported.

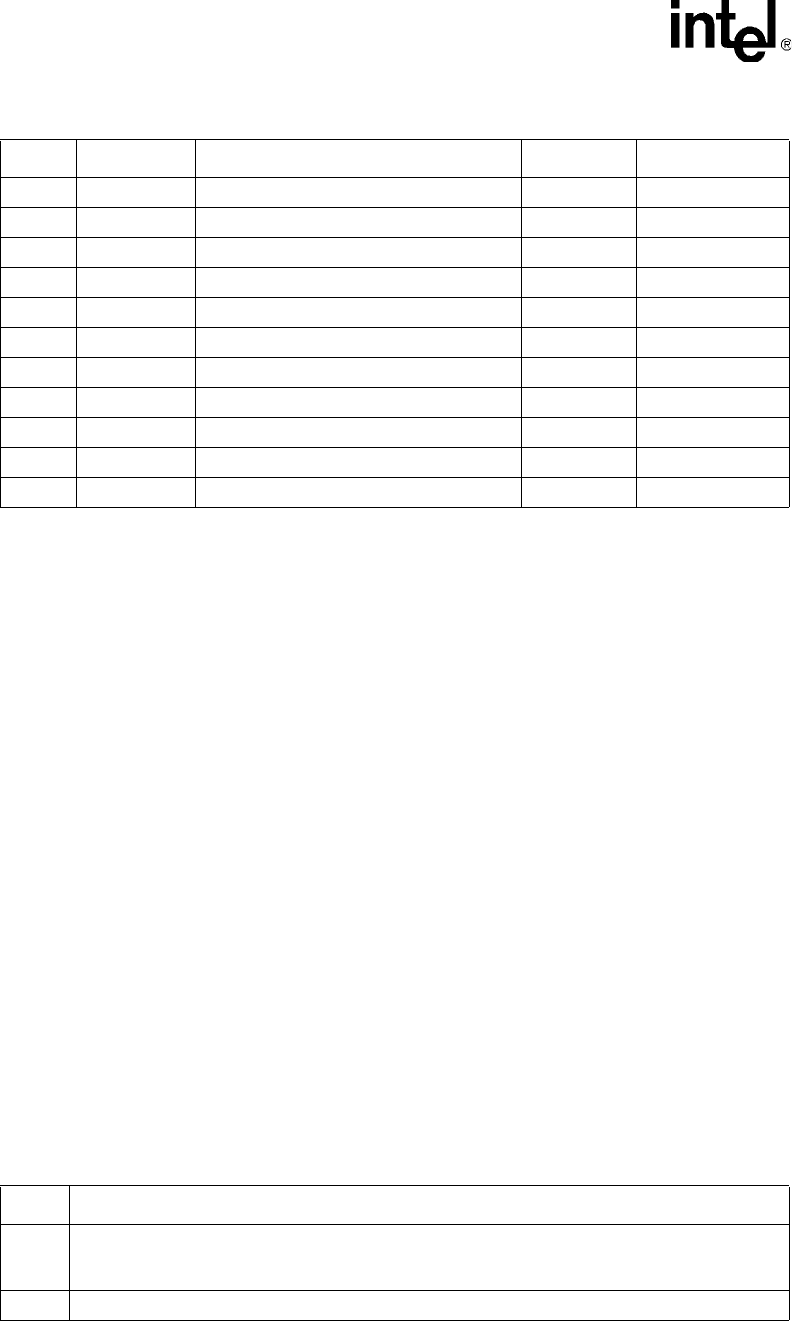

58h PI2_PICB PCM In 2 Position in Current Buffer 0000h RO

5Ah PI2_PIV PCM In 2 Prefetched Index Value 00h RO

5Bh PI2_CR PCM In 2 Control 00h R/W, R/W (special)

60h SPBAR S/PDIF Buffer Descriptor List Base Address 00000000h R/W

64h SPCIV S/PDIF Current Index Value 00h RO

65h SPLVI S/PDIF Last Valid Index 00h R/W

66h SPSR S/PDIF Status 0001h R/WC, RO

68h SPPICB S/PDIF Position In Current Buffer 0000h RO

6Ah SPPIV S/PDIF Prefetched Index Value 00h RO

6Bh SPCR S/PDIF Control 00h R/W, R/W (special)

80h SDM SData_IN Map 00h R/W, RO

Table 2-3. Native Audio Bus Master Control Registers (Sheet 2 of 2)

Offset Mnemonic Name Default Access

Bit Description

31:3

Buffer Descriptor Base Address[31:3] — R/W. These bits represent address bits 31:3. The data

should be aligned on 8-byte boundaries. Each buffer descriptor is 8 bytes long and the list can

contain a maximum of 32 entries.

2:0 Hardwired to 0.