Programmer’s Reference Manual 79

AC ’97 Audio Controller Registers (D30:F2)

2.2.2 x_CIV—Current Index Value Register (Audio—D30:F2)

I/O Address: NABMBAR + 04h (PICIV), Attribute: RO

NABMBAR + 14h (POCIV),

NABMBAR + 24h (MCCIV)

MBBAR + 44h (MC2CIV)

MBBAR + 54h (PI2CIV)

MBBAR + 64h (SPCIV)

Default Value: 00h Size: 8 bits

Lockable: No Power Well: Core

Software can read the registers at offsets 04h, 05h and 06h simultaneously by performing a single,

32-bit read from address offset 04h. Software can also read this register individually by doing a

single, 8-bit read to offset 04h.

NOTE: Reads across DWord boundaries are not supported.

2.2.3 x_LVI—Last Valid Index Register (Audio—D30:F2)

I/O Address: NABMBAR + 05h (PILVI), Attribute: R/W

NABMBAR + 15h (POLVI),

NABMBAR + 25h (MCLVI)

MBBAR + 45h (MC2LVI)

MBBAR + 55h (PI2LVI)

MBBAR + 65h (SPLVI)

Default Value: 00h Size: 8 bits

Lockable: No Power Well: Core

Software can read the registers at offsets 04h, 05h and 06h simultaneously by performing a single,

32-bit read from address offset 04h. Software can also read this register individually by doing a

single, 8-bit read to offset 05h.

NOTE: Reads across DWord boundaries are not supported.

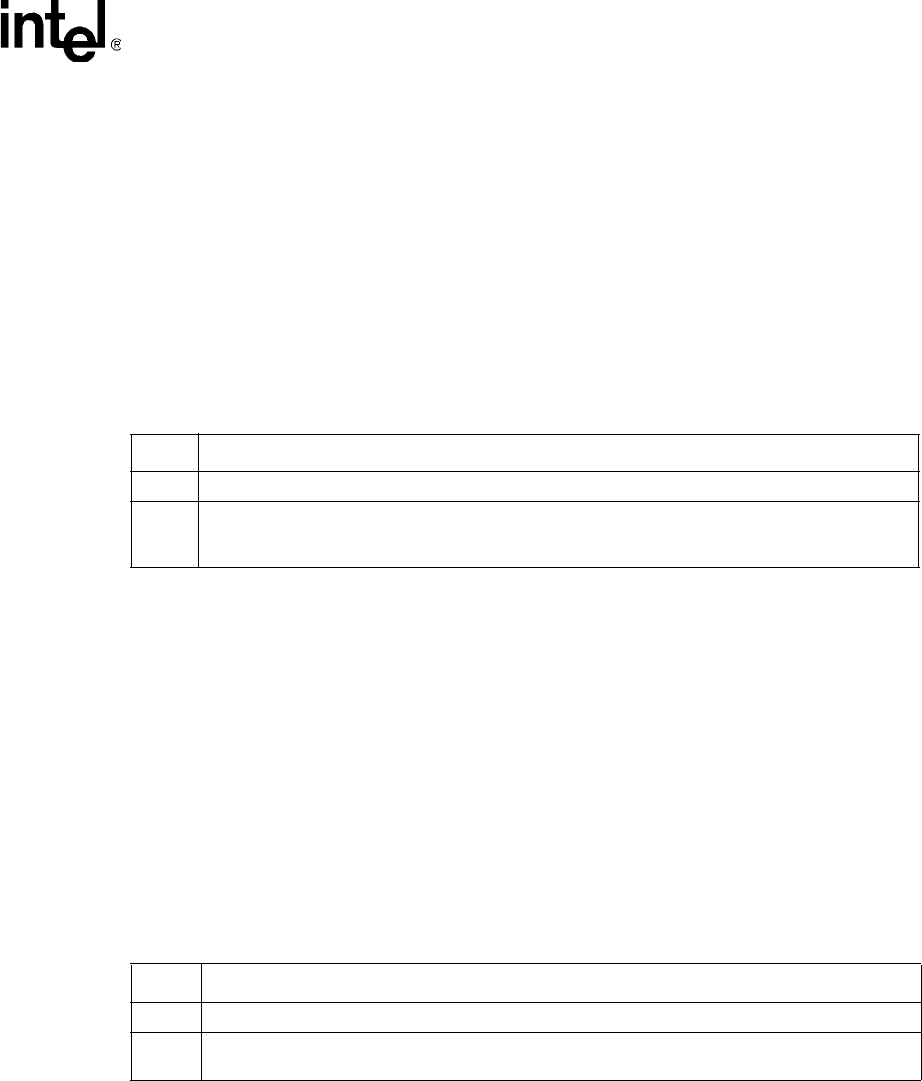

Bit Description

7:5 Hardwired to 0

4:0

Current Index Value [4:0] — RO. These bits represent which buffer descriptor within the list of 32

descriptors is currently being processed. As each descriptor is processed, this value is incremented.

The value rolls over after it reaches 31.

Bit Description

7:5 Hardwired to 0.

4:0

Last Valid Index [4:0] — R/W. This value represents the last valid descriptor in the list. This value is

updated by the software each time it prepares a new buffer and adds it to the list.