Programmer’s Reference Manual 77

AC ’97 Audio Controller Registers (D30:F2)

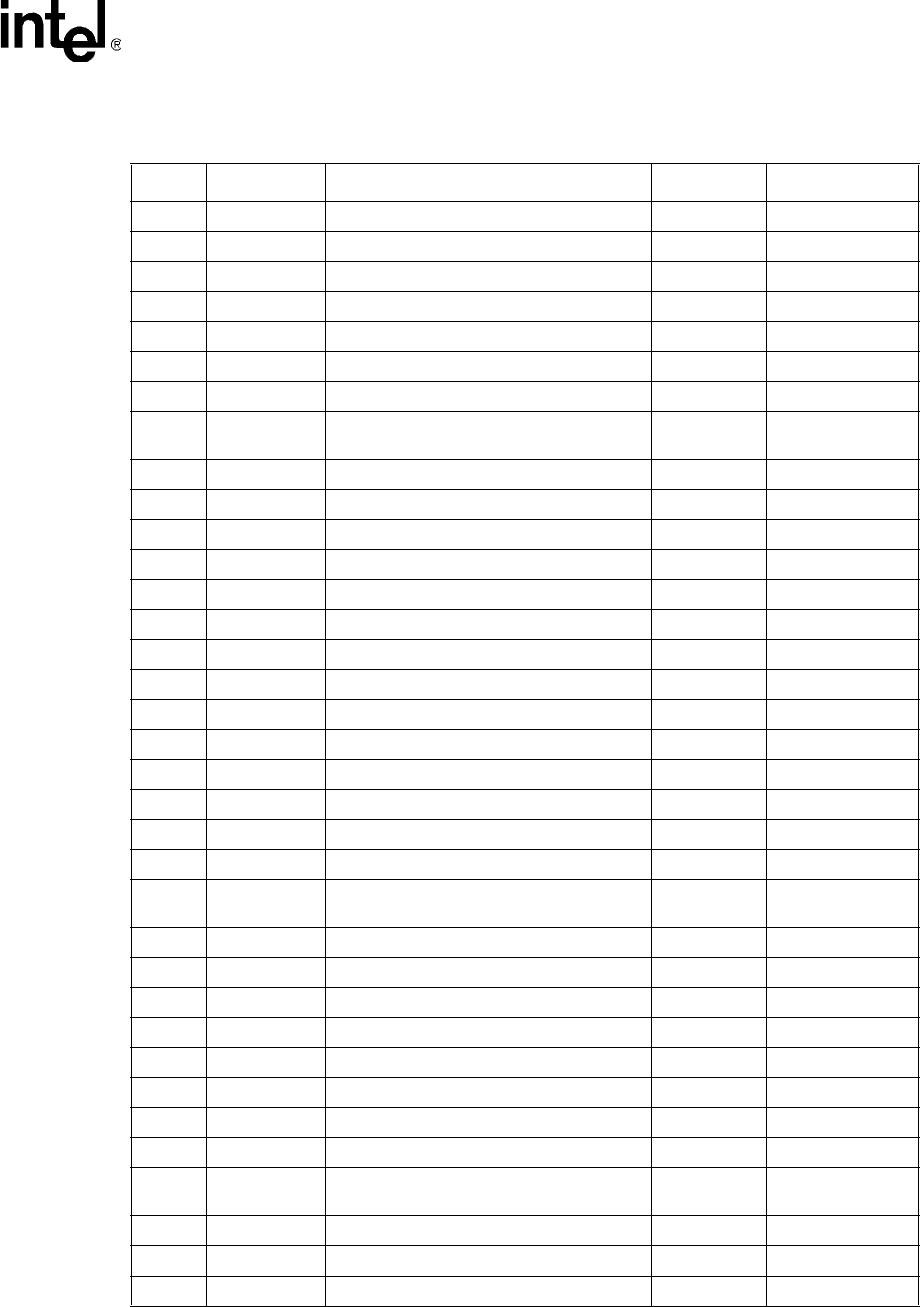

Table 2-3. Native Audio Bus Master Control Registers (Sheet 1 of 2)

Offset Mnemonic Name Default Access

00h PI_BDBAR PCM In Buffer Descriptor list Base Address 00000000h R/W

04h PI_CIV PCM In Current Index Value 00h RO

05h PI_LVI PCM In Last Valid Index 00h R/W

06h PI_SR PCM In Status 0001h R/WC, RO

08h PI_PICB PCM In Position in Current Buffer 0000h RO

0Ah PI_PIV PCM In Prefetched Index Value 00h RO

0Bh PI_CR PCM In Control 00h R/W, R/W (special)

10h PO_BDBAR

PCM Out Buffer Descriptor list Base

Address

00000000h R/W

14h PO_CIV PCM Out Current Index Value 00h RO

15h PO_LVI PCM Out Last Valid Index 00h R/W

16h PO_SR PCM Out Status 0001h R/WC, RO

18h PO_PICB PCM In Position In Current Buffer 0000h RO

1Ah PO_PIV PCM Out Prefetched Index Value 00h RO

1Bh PO_CR PCM Out Control 00h R/W, R/W (special)

20h MC_BDBAR Mic. In Buffer Descriptor List Base Address 00000000h R/W

24h MC_CIV Mic. In Current Index Value 00h RO

25h MC_LVI Mic. In Last Valid Index 00h R/W

26h MC_SR Mic. In Status 0001h R/WC, RO

28h MC_PICB Mic. In Position In Current Buffer 0000h RO

2Ah MC_PIV Mic. In Prefetched Index Value 00h RO

2Bh MC_CR Mic. In Control 00h R/W, R/W (special)

2Ch GLOB_CNT Global Control 00000000h R/W, R/W (special)

30h GLOB_STA Global Status

See register

description

R/W, R/WC, RO

34h CAS Codec Access Semaphore 00h R/W (special)

40h MC2_BDBAR Mic. 2 Buffer Descriptor List Base Address 00000000h R/W

44h MC2_CIV Mic. 2 Current Index Value 00h RO

45h MC2_LVI Mic. 2 Last Valid Index 00h R/W

46h MC2_SR Mic. 2 Status 0001h RO, R/WC

48h MC2_PICB Mic 2 Position In Current Buffer 0000h RO

4Ah MC2_PIV Mic. 2 Prefetched Index Value 00h RO

4Bh MC2_CR Mic. 2 Control 00h R/W, R/W (special)

50h PI2_BDBAR

PCM In 2 Buffer Descriptor List Base

Address

00000000h R/W

54h PI2_CIV PCM In 2 Current Index Value 00h RO

55h PI2_LVI PCM In 2 Last Valid Index 00h R/W

56h PI2_SR PCM In 2 Status 0001h R/WC, RO