123

ROW 1

BYTES

ROW 2

BYTES

ROW 3

BYTES

ROW 4

BYTES

ROW 5

BYTES

ROW 6

BYTES

ROW 7

BYTES

ROW 8

BYTES

ROW 9

BYTES

B1 B2 B3 B4 B5 B6 B7 B8 B1 B2 B3 B4 B5 B6 B7 B8 B1 B2 B3 B4 B5 B6 B7 B8

B1 B2 B3 B4 B5 B6 B7 B8 B1 B2 B3 B4 B5 B6 B7 B8 B1 B2 B3 B4 B5 B6 B7 B8

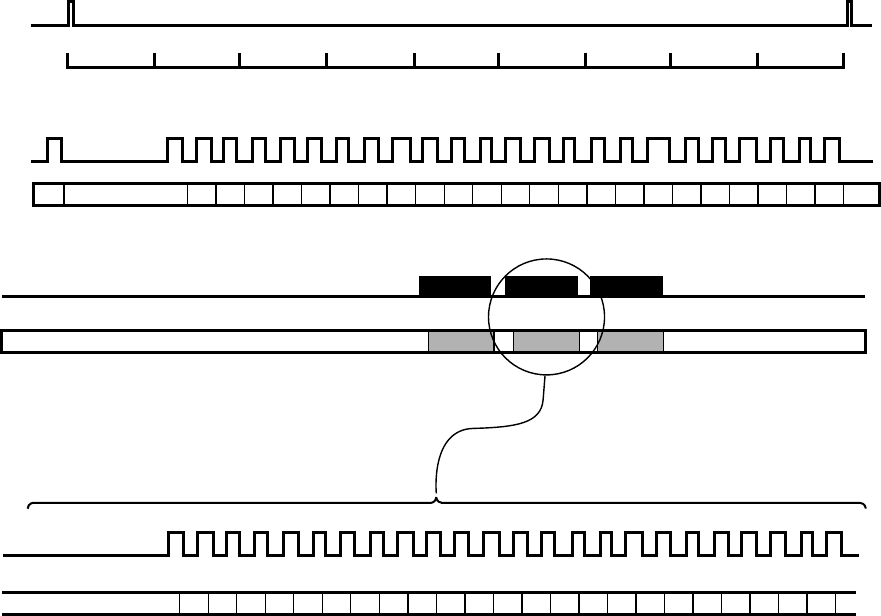

RX_FRAME_SFP

RX_SDCC_CLK

RX_SDCC_DATA

RX_LDCC_CLK

RX_LDCC_DATA

APPROX. 2M RX_LDCC_CLK

RX_LDCC_CLK

RX_LDCC_DATA

Figure 46. Receive Data Link Clock and Data Alignment

The receive data link clock and data alignment timing diagram (Figure 46) shows the relationship between

the RX_SDCC_DATA, and RX_LDCC_DATA serial data outputs, and their associated clocks,

RX_SDCC_CLK and RX_LDCC_CLK. RX_SDCC_CLK is a 216 kHz, 50% duty cycle clock that is gapped

to produce a 192 kHz nominal rate that is aligned with ROFP as shown. RX_LDCC_CLK is a 2.16 MHz,

67% (high) / 33% (low) duty cycle clock that is gapped to produce a 576 kHz nominal rate that is aligned with

RX_FRAME_SFP as shown above. RX_SDCC_DATA (RX_LDCC_DATA) is updated on the falling

RX_SDCC_CLK (RX_LDCC_CLK) edge.