88

Bits 7-3: Reserved

Bit 2: RX_DES_INH is set to inhibit the descrambling (X

43

+1) of the RX Payload Data sent from the

SPE/VC Extractor in the SONET/SDH portion. Removal of the GFP core header DC balancing is

still performed.

Bit 1: RX_FCS_INH is set to inhibit the checking of the LAPS/GFP 32-bit FCS field. In GFP mode, the

optional FCS is assumed to be present but the checking of this field is inhibited.

Bit 0: RX_FCS_REM_INH is set to inhibit the 32-bit FCS field removal. When set, the FCS field is not

removed and so is passed on to the RX FIFO. In GFP mode, this bit should be set when the

optional FCS field is not appended to the end of the frame.

5.6 Ethernet Receive Registers

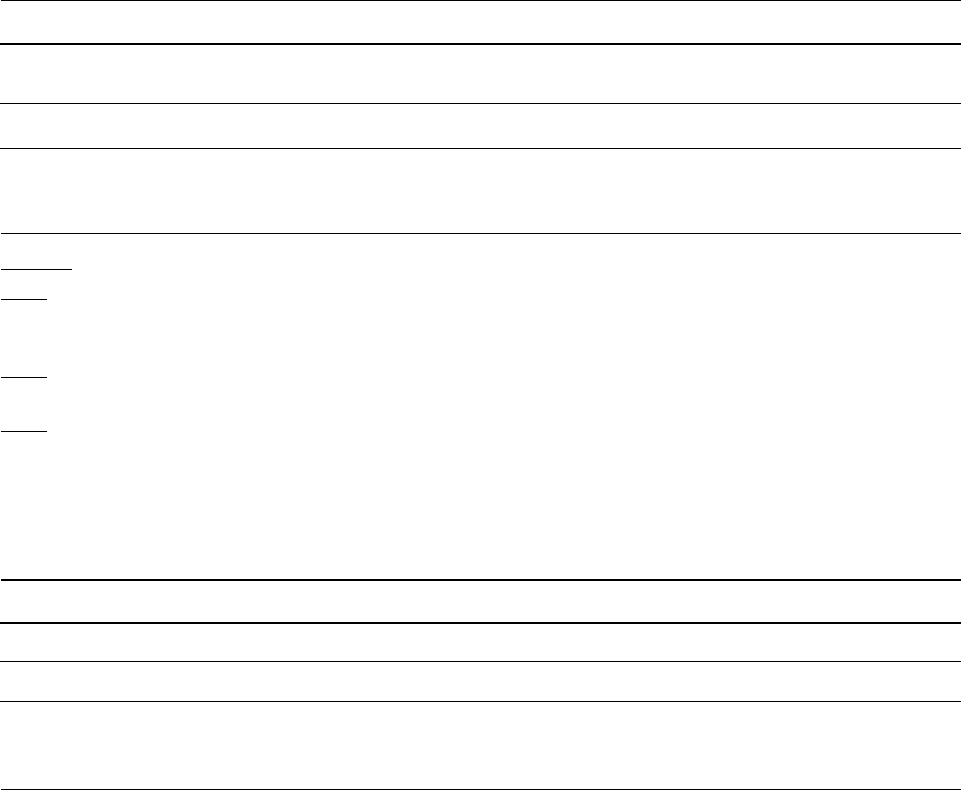

ADDR = 0x1C0: GFP/LAPS Mode

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bit name Reserved Reserved Reserved Reserved Reserved RX_DES_ RX_FCS_ RX_FCS_

INH INH REM_INH

R/W — ——— — R/W R/W R/W

Value 0000 000 0

after

reset

Bits 7-0: RX_FIFO_THRESHOLD[7:0] is the LSB of the RX-FIFO Transmit Threshold which is used by

the INFO FIELD RX FIFO Controller to determine when it starts to read the data from the RX

FIFO. For frames whose size is greater than the programmed RX_FIFO_THRESHOLD, the

INFO FIELD RX FIFO Controller begins to read data out of the RX FIFO when the number of bytes

of the portion of the receiving frame that has been stored into the RX FIFO is equal to or greater

than the programmed RX_FIFO_THRESHOLD. The default value is 420 bytes (0x01A4).

In LAPS mode, for jumbo frame support, increase this value to 1150 (0x47E). In GFP mode, set

this value to 20 (0x14).

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bit name RX_FIFO_THRESHOLD[7:0]

R/W R/W

Value 0xA4

after

reset

ADDR = 0x1C2: RX-FIFO Transmit Threshold