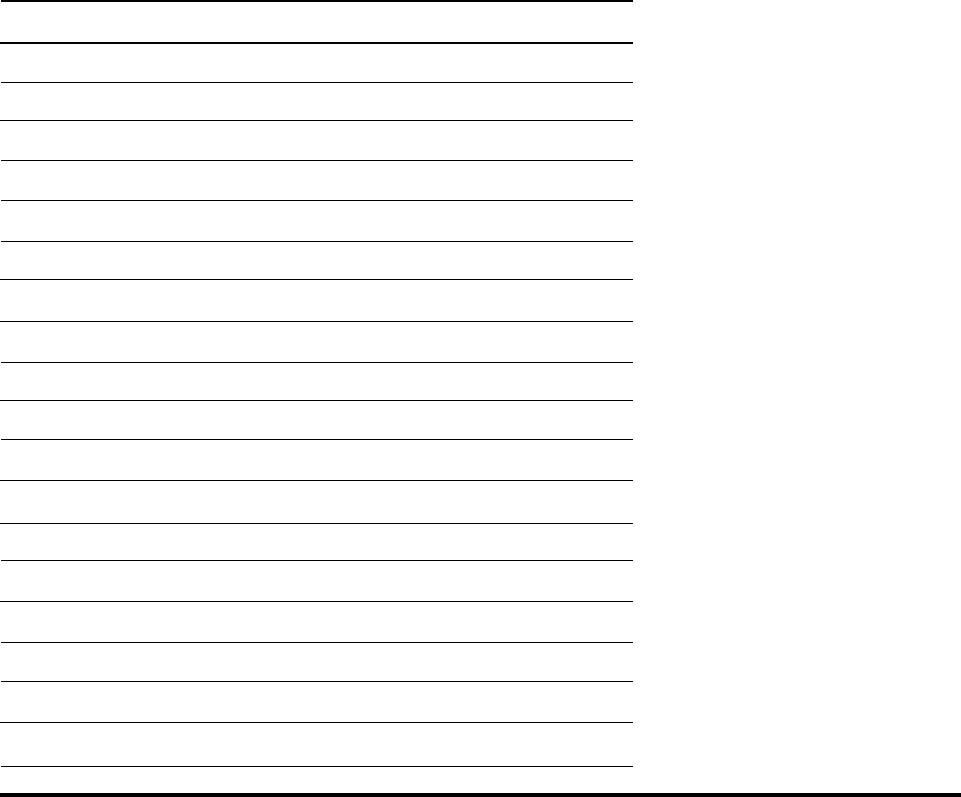

48

Address Register Name

0x1CF Receive Spare Field Byte

0x1D0 Receive Pre-Sync States

0x1D1-0x1D2 Receive SAPI Field

0x1D3 Reserved

0x1D4-0x1D7 Receive MII Frames Transmitted OK

0x1D8-0x1DB Receive FCS and HEC Error Counter

0x1DC-0x1DF Receive Format and Destination Error Counter

0x1E0-0x1E3 Receive Out of Sync Error Counter

0x1E4-0x1E7 Receive FIFO Overflow Error

0x1E8-0x1EB Receive FIFO Underrun Error

0x1EC Ethernet Receive Interrupt Event

0x1ED Ethernet Receive Interrupt Mask

0x1EF Receive Minimum Frame Size

0x1F0-0x1F1 Receive Maximum Frame Size

0x1F2-0x1F3 Reserved

0x1F4-0x1F7 Receive Minimum Frame Size Violations

0x1F8-0x1FB Receive Maximum Frame Size Violations

0x1FC-0x1FF Reserved

In the register definition tables in

the following sections, NAMES of

the registers are specified in

abbreviated format.

Read/Write is specified using:

“R/W” – Read/Write, for registers

that are both readable and

writable.

“RO” – Read Only, for registers

that are readable only.

“W1C” – Write-1-to-Clear, for reg-

isters that can be cleared when a

one is written by firmware. The

next read access to this register

returns zero to firmware because

the one acts as a command to per-

form the required clear function.

“W1S” – Write-1-to-Set, for regis-

ters that can be set or asserted

when a one is written. The next

read access to this register re-

turns a one.

DEFAULT is the value of the reg-

isters when either a hard or soft

reset occurs.