92

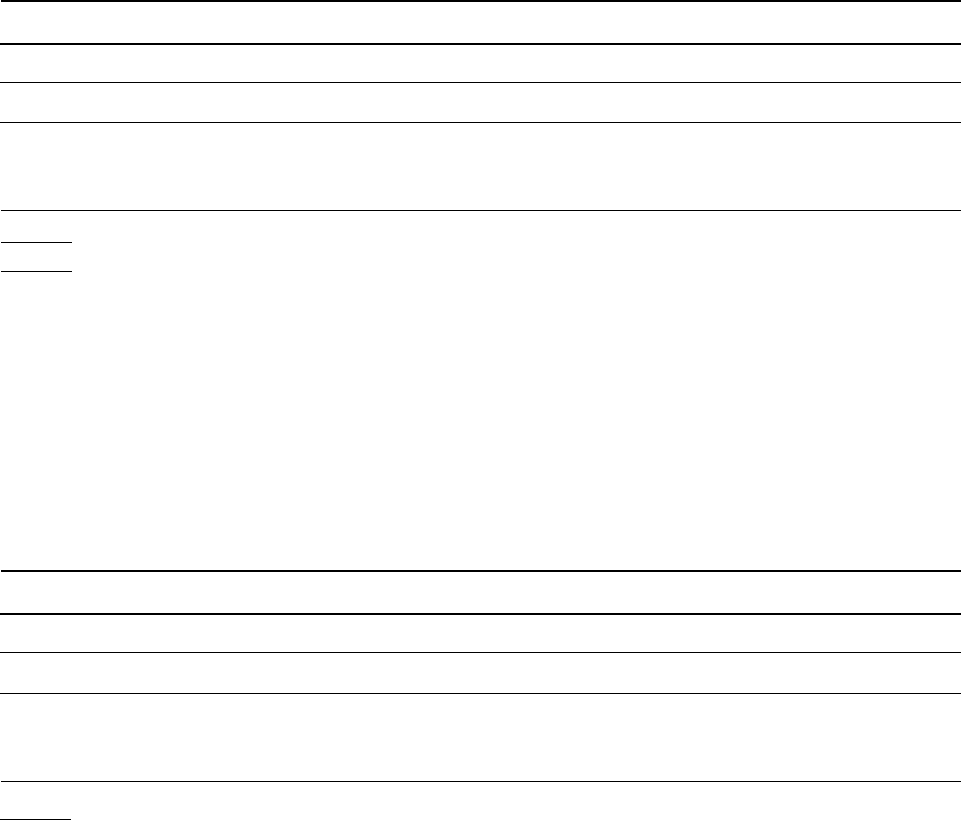

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bit name Reserved Reserved Reserved LOW_IFG[4:0]

R/W —— —R/W

Value 0 0 0 0x0A

after

reset

ADDR = 0x1C9: Low Inter-Frame-Gap

Bits 7-5: Reserved

Bits 4-0: LOW_IFG[4:0] specifies the Low Inter-Frame-Gap which is used by the MII RX interface to insert

the minimum number of idle cycles between two MAC frames sent out onto the MII RX bus. This

value is used when the INFO FIELD RX FIFO Controller sets the IFG Selection Mode (IFG_SEL)

to Low- IFG and sends it to MII RX interface. When the number of bytes in the RX FIFO becomes

greater than or equal to the High Inter-Frame-Gap Water Mark, IFG_SEL is set to one for Low-IFG.

When the number of bytes in the RX FIFO becomes less than or equal to the Low Inter-Frame-Gap

Water Mark, IFG_SEL is set to zero for Normal-IFG. At power-up, IFG_SEL defaults to zero for

Normal-IFG selection. This value remains zero until the number of bytes in the RX FIFO becomes

greater than or equal to the programmable High Inter-Frame-Gap Water Mark.

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bit name RX_ADR_TYPE_L [7:0]

R/W R/W

Value 0x04

after

reset

ADDR = 0x1CA: Receive ADR/TYPE_L

Bits 7-0: RX_ADR_TYPE_L [7:0] specifies the expected address when in LAPS mode or the expected

LSB of the Type field when in GFP mode, which consists of the Payload Identifier. The LAPS or

GFP RX Processor compares the received SAPI/TYPE to this value when the

RX_SAPI_CHECK_INH or RX_TYPE_CHECK_INH is not set, respectively. If the comparison fails,

the frame is discarded. The default value is assigned to 0x04 for LAPS since LAPS is the default

mode. For GFP mode, this register should be programmed to 0x01 for Ethernet payload.