63

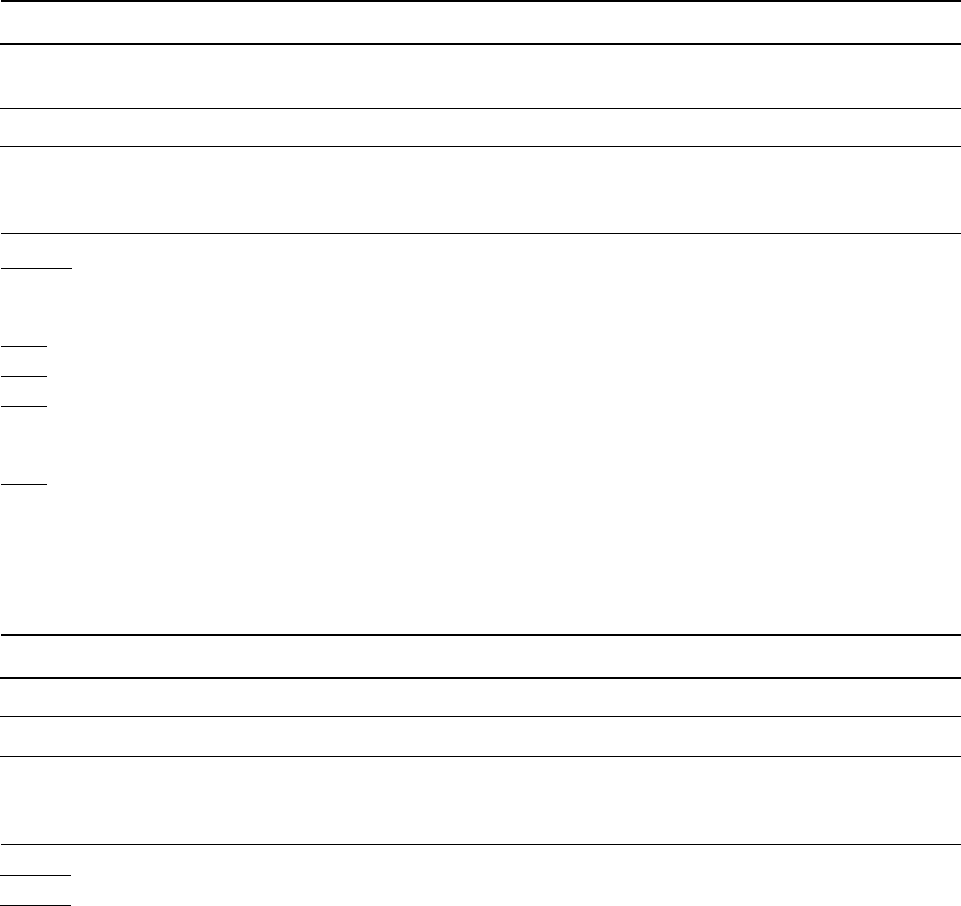

ADDR=0x0FF: Receive TOH Monitor Control

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bit name K2_CONSEC_NUM[3:0] RX_LOS_ RX_LOS_ RX_FRAM_ RX_LOF_

LEVEL INH INH ALG

R/W R/W R/W R/W R/W R/W

Value 01010000

after

reset

Bits 7-4: K2_CONSEC_NUM[3:0]: This 4 bit register is used to keep track of the number of consecutive

occurrences of LAIS and LRDI in order for the presence/absence of LAIS or LRDI to be detected

and the monitors to be updated accordingly.

Bit 3: RX_LOS_LEVEL is set to indicate RX_LOS is active low.

Bit 2: RX_LOS_INH is set to inhibit the contribution of RX_LOS to LRDI.

Bit 1: RX_FRAM_INH: If 1, the HDMP-3001 receive framer is enable and the parallel input signal is not

assumed to be byte aligned. If 0, the receive framer in the HDMP-3001 is bypassed, and it requires

a frame start condition, RX_FRAME_IN, as well as data and clock.

Bit 0: RX_LOF_ALG: If 1, RX_LOF will be cleared after RX_OOF is inactive for 8 consecutive frames.

If 0, RX_LOF will be cleared after RX_OOF is inactive for 24 consecutive frames.

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Bit name Reserved Reserved Reserved Reserved RX_FRAME_POSITION[3:0]

R/W ————R/W

Value 000000 0 0

after

reset

ADDR=0x101: Receive Framer Position Control

Bits 7-4: Reserved

Bits 3-0: RX_FRAME_POSITION [3:0] – These four bits control the relationship between the data

bytes on the input bus RX_DATA [7:0] and the RX_FRAME_IN clock pulse. Please refer to

Table 21.