Rev. 1.0, 07/01, page 175 of 372

12.6 Usage Notes

The following types of contention or operation can occur in timer W operation.

1. The pulse width of the input clock signal and the input capture signal must be at least two

system clock(φ) cycles; shorter pulses will not be detected correctly.

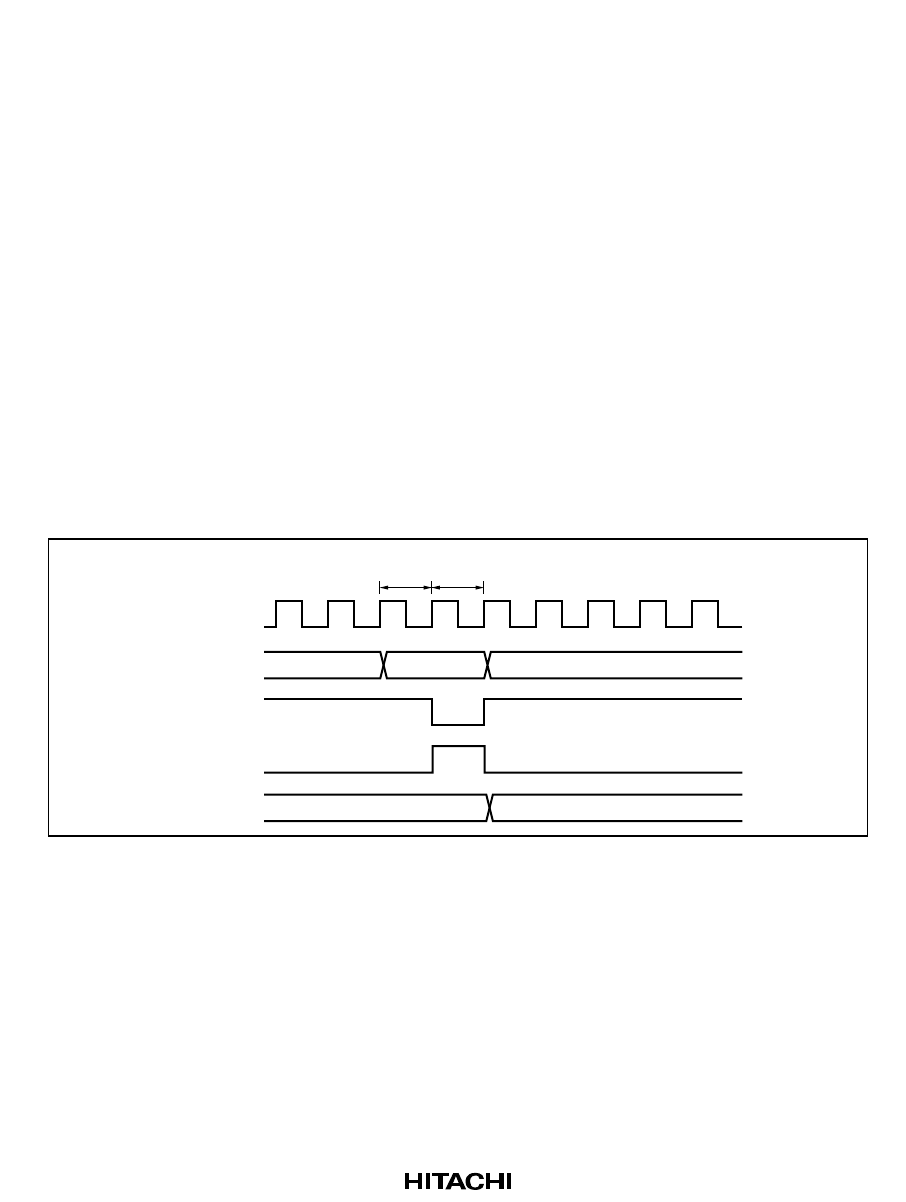

2. Writing to registers is performed in the T2 state of a TCNT write cycle.

If counter clear signal occurs in the T2 state of a TCNT write cycle, clearing of the counter

takes priority and the write is not performed, as shown in figure 12-24. If counting-up is

generated in the TCNT write cycle to contend with the TCNT counting-up, writing takes

precedence.

3. Depending on the timing, TCNT may be incremented by a switch between different internal

clock sources. When TCNT is internally clocked, an increment pulse is generated from the

rising edge of an internal clock signal, that is divided system clock (φ). Therefore, as shown in

figure 12-25 the switch is from a low clock signal to a high clock signal, the switchover is seen

as a rising edge, causing TCNT to increment.

4. If timer W enters module standby mode while an interrupt request is generated, the interrupt

request cannot be cleared. Before entering module standby mode, disable interrupt requests.s

Counter clear

signal

Write signal

Address

φ

TCNT address

TCNT

TCNT write cycle

T1 T2

N H'0000

Figure 12-24 Contention between TCNT Write and Clear