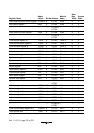

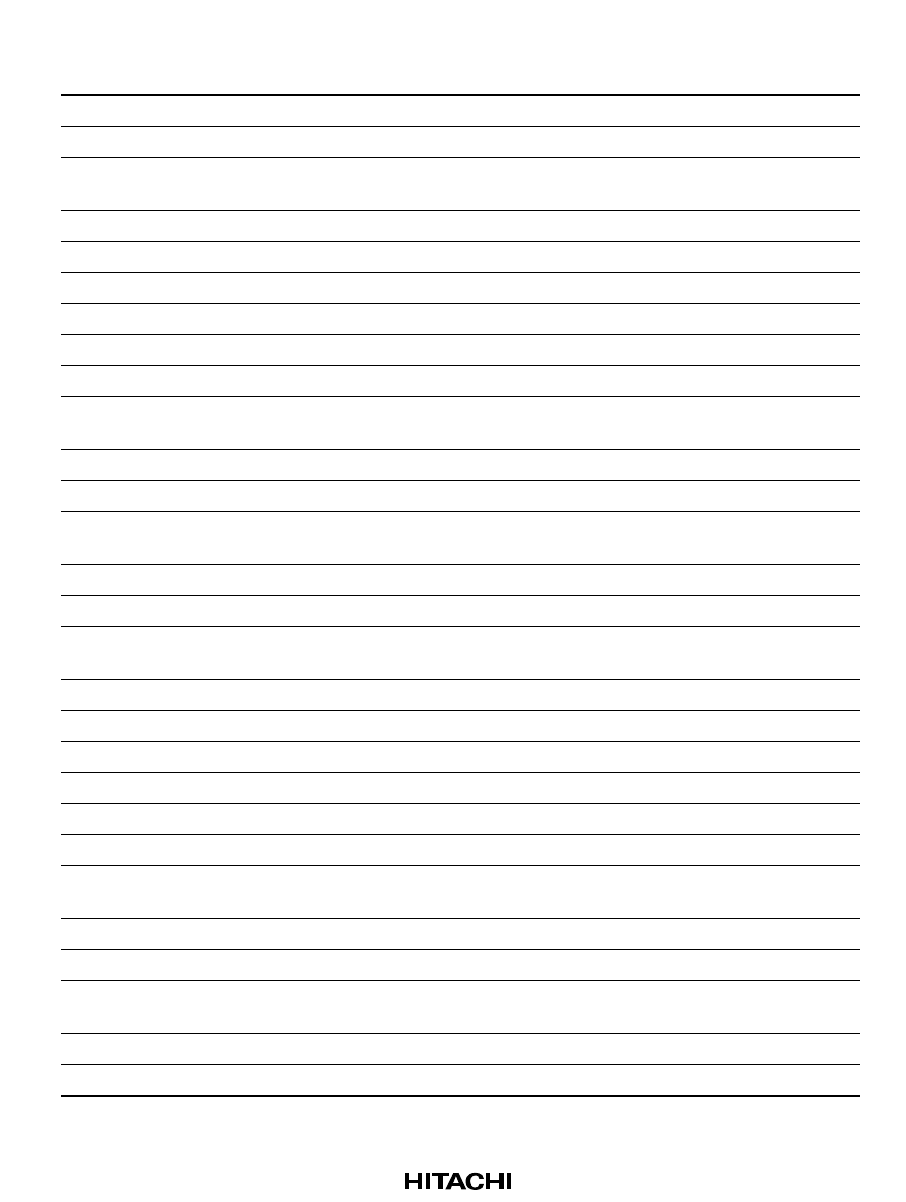

Rev. 1.0, 07/01, page 277 of 372

Register Name

Abbre-

viation Bit No Address

Module

Name

Data

Bus

Width

Access

State

Timer mode register WD TMWD 8 H'FFC2 WDT*

3

82

———

H'FFC3

———

———

H'FFC4 to

H'FFC7

———

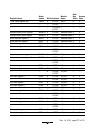

Address break control register ABRKCR 8 H'FFC8 Address break 8 2

Address break status register ABRKSR 8 H'FFC9 Address break 8 2

Break address register H BARH 8 H'FFCA Address break 8 2

Break address register L BARL 8 H'FFCB Address break 8 2

Break data register H BDRH 8 H'FFCC Address break 8 2

Break data register L BDRL 8 H'FFCD Address break 8 2

———

H'FFCE,

H'FFCF

———

Port pull-up control register 1 PUCR1 8 H'FFD0 I/O port 8 2

Port pull-up control register 5 PUCR5 8 H'FFD1 I/O port 8 2

———

H'FFD2,

H'FFD3

I/O port

——

Port data register 1 PDR1 8 H'FFD4 I/O port 8 2

Port data register 2 PDR2 8 H'FFD5 I/O port 8 2

——

8 H'FFD6,

H'FFD7

I/O port

——

Port data register 5 PDR5 8 H'FFD8 I/O port 8 2

———

H'FFD9 I/O port

——

Port data register 7 PDR7 8 H'FFDA I/O port 8 2

Port data register 8 PDR8 8 H'FFDB I/O port 8 2

———

H'FFDC I/O port

——

Port data register B PDRB 8 H'FFDD I/O port 8 2

———

H'FFDE,

H'FFDF

I/O port

——

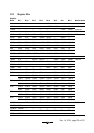

Port mode register 1 PMR1 8 H'FFE0 I/O port 8 2

Port mode register 5 PMR5 8 H'FFE1 I/O port 8 2

———

H'FFE2,

H'FFE3

I/O port

——

Port control register 1 PCR1 8 H'FFE4 I/O port 8 2

Port control register 2 PCR2 8 H'FFE5 I/O port 8 2