Rev. 1.0, 07/01, page 76 of 372

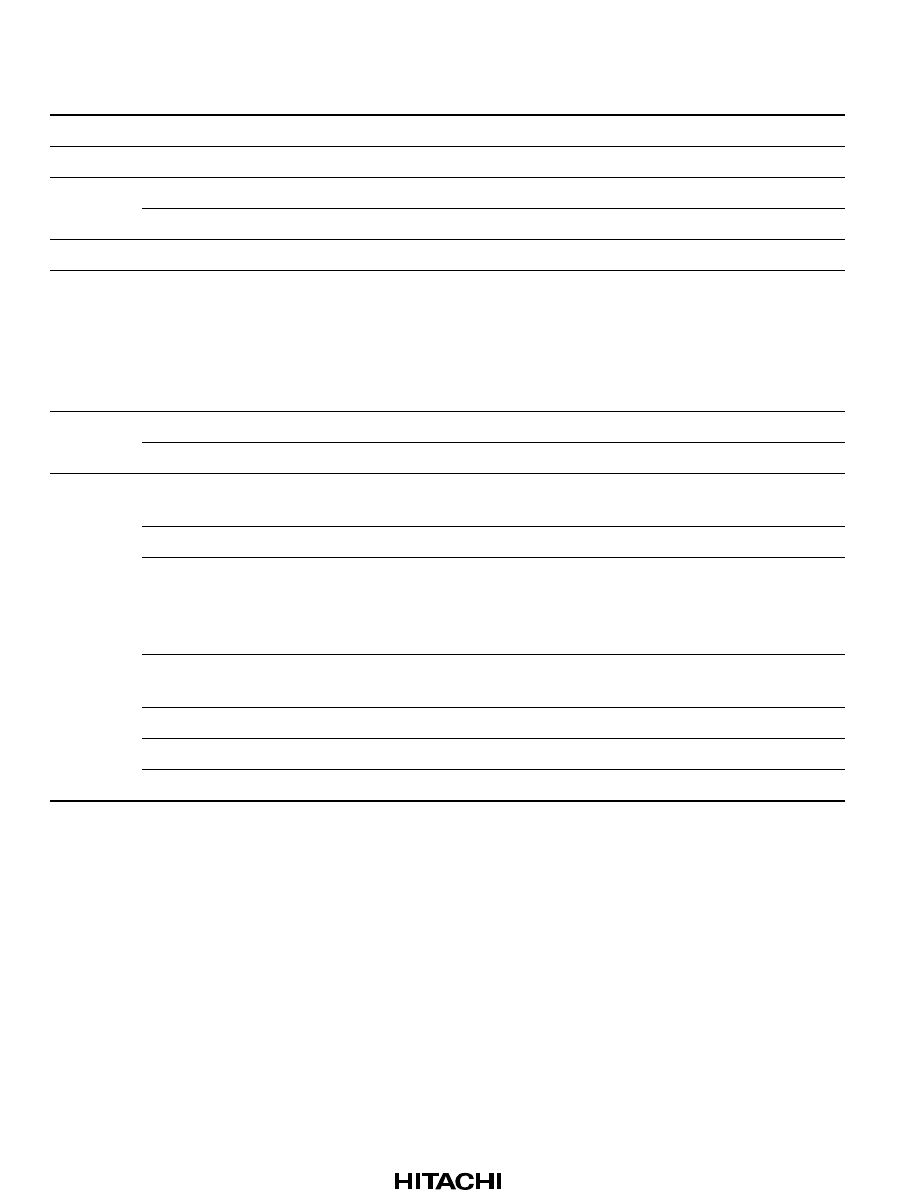

Table 6-3 Internal State in Each Operating Mode

Function Active Mode Sleep Mode

Subactive

Mode

Subsleep

Mode Standby Mode

System clock oscillator Functioning Functioning Halted Halted Halted

Subclock oscillator Functioning Functioning Functioning Functioning Functioning

Instructions Functioning Halted Functioning Halted HaltedCPU

operations

Registers Functioning Retained Functioning Retained Retained

RAM Functioning Retained Functioning Retained Retained

IO ports Functioning Retained Functioning Retained Register

contents are

retained, but

output is the

high-impedance

state.

IRQ3 to IRQ0 Functioning Functioning Functioning Functioning FunctioningExternal

interrupts

WKP5 to WKP0 Functioning Functioning Functioning Functioning Functioning

Timer A Functioning Functioning Functioning if the timekeeping time-base

function is selected, and retained if not selected

Timer V Functioning Functioning Reset Reset Reset

Timer W Functioning Functioning Retained(if internal clock

φ

is

selected as a count clock, the

counter is incremented by a

subclock

*

)

Retained

Watchdog timer Functioning Functioning Retained(functioning if the internal oscillator is

selected as a count clock

*

)

SCI3 Functioning Functioning Reset Reset Reset

IIC2 Functioning Functioning Retained

*

Retained Retained

Peripheral

functions

A/D converter Functioning Functioning Reset Reset Reset

Note:

*

Registers can be read or written in subactive mode.

6.2.1 Sleep Mode

In the sleep mode, CPU operation is halted but the on-chip peripheral modules function at the

clock frequency set by the MA2, MA1, and MA0 bits in SYSCR2. CPU register contents are

retained. When an interrupt is requested, the sleep mode is cleared and interrupt exception

handling starts. The sleep mode is not cleared if the I bit of the condition code register (CCR) is

set to 1 or the requested interrupt is disabled in the interrupt enable register. After the sleep mode

is cleared, a transition is made to active mode when the LSON bit in SYSCR2 is 0, and a transition

is made to subactive mode when the bit is 1.