Theory of Operation Teledyne API - Model 200EH/EM Operation Manual

210

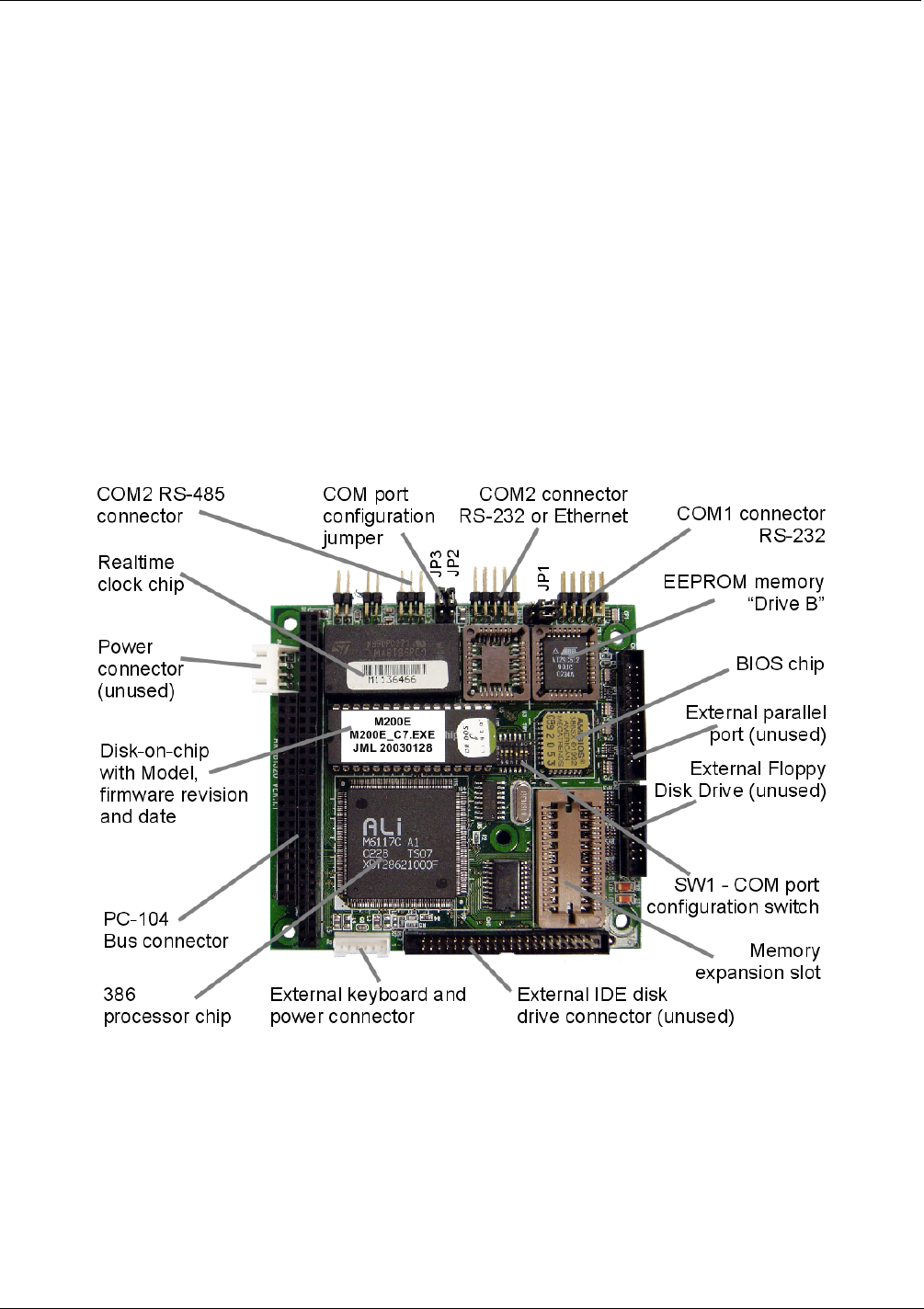

10.4.1. CPU

The CPU is a low power (5 VDC, 0.8A max), high performance, 386-based microcomputer running a version of

the DOS operating system. Its operation and assembly conform to the PC-104 specification, version 2.3 for

embedded PC and PC/AT applications. It has 2 MB of DRAM memory on board and operates at 40 MHz clock

rate over an internal, 32-bit data and address bus. Chip to chip data handling is performed by two 4-channel,

direct memory access (DMA) devices over data busses of either 8-bit or 16-bit bandwidth. The CPU supports

both RS-232 and RS-485 serial protocols. Figure 10-10-17 shows

the CPU board.

The CPU communicate

s with the user and the outside world in a variety of ways:

Through the analyzer’s keyboard and vacuum fluorescence display over a clocked, digital, serial I/O bus

using the I

2

C protocol (read I-square-C bus)

RS-232 and/or RS-485 serial ports (one of which can be connected to an Ethernet converter)

Various analog voltage and current outputs

Several digital I/O channels

Figure 10-10-17: M200EH/EM CPU Board Annotated

Finally, the CPU issues commands (also over the I2C bus) to a series of relays and switches located on a

separate printed circuit assembly, the relay board (located in the right rear of the chassis on its own mounting

bracket) to control the function of heaters and valves. The CPU includes two types of non-volatile data storage,

one disk-on-chip and one or two flash chips.

04521C (DCN5731)