1

2

3

4

5 6

A

B

C

D

6

5

4

3

2

1

D

C

B

A

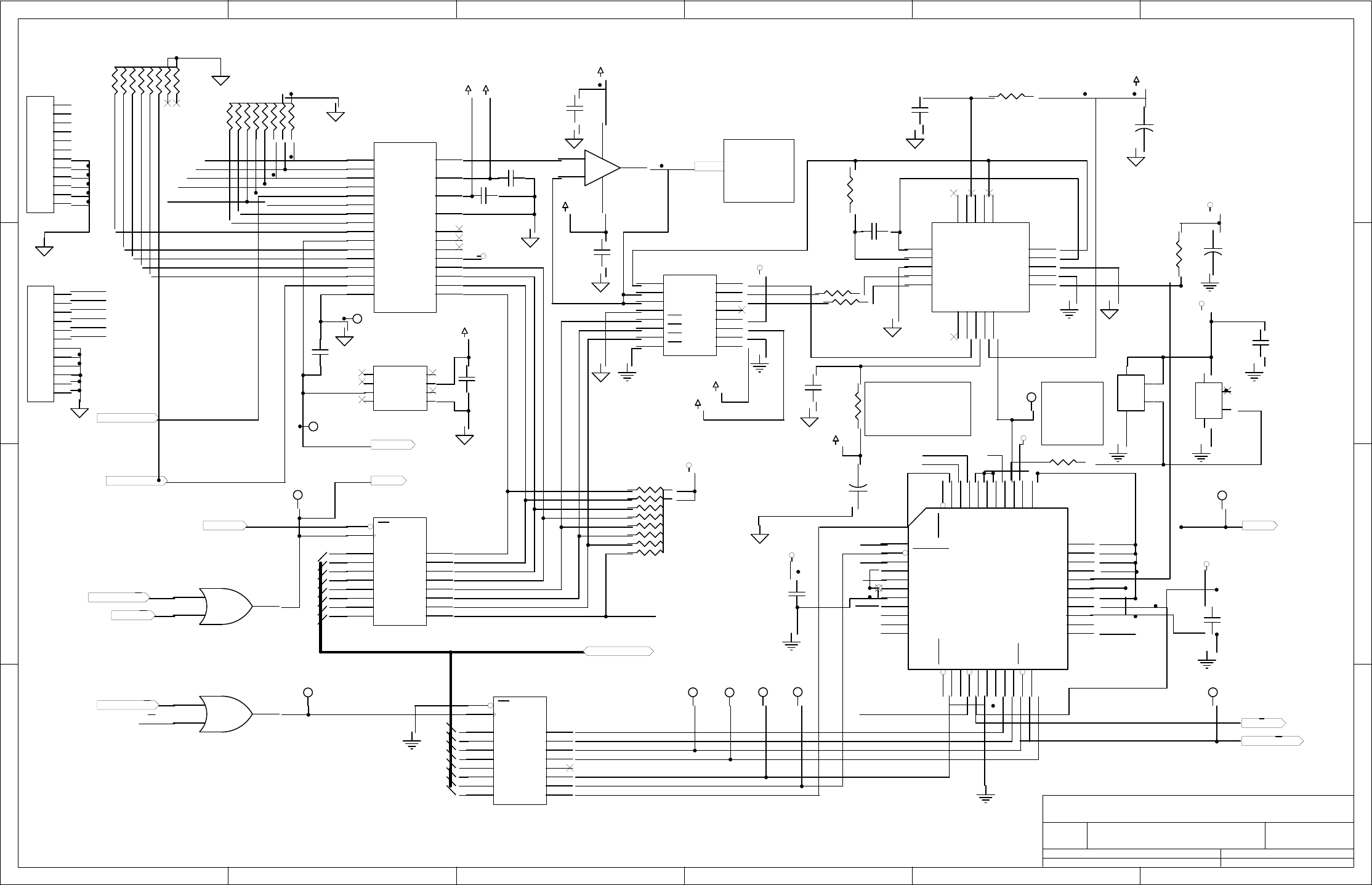

Title

Number RevisionSize

Orcad B

Date: 17-Jun-2008 Sheet of

File: N:\Pcbmgr\05701dn.E-motherboard.gen4\Source\05701a.DDBDrawn By:

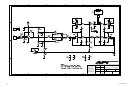

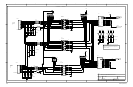

IOW

CH1

CH3

CH4

CH7

CH8

CH9

CH12

CH13

CH14

SB

MID

SA

SC

MSB

D4

D0

D3

D6

LSB

START

D7

SEL60

D5

SEL60

CH2

CH11

D4

D3

D6

D4

D1

D2

D2

D0

D3

D1

D5

D2

D1

D7

D7

D0

D5

D6

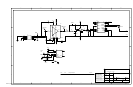

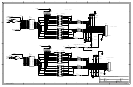

1

TP50

3

4

6

1

X2

JITO-2-DCA5AE-4.8MHZ

+

C41

10 uF, 35V, TANTALUM

1

TP52

1

2

3

4

5

6

7

8

9

10

11

12

J110

MICROFIT-12

C51

0.15 uF, ceramic

C42

0.15 uF, ceramic

R46

1.1K, 5%

C47

1.2 uF, 6.3V ceramic

1

TP48

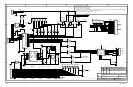

IN 16

4

IN 15

5

IN 14

6

IN 13

7

IN 12

8

IN 11

9

IN 10

10

IN 9

11

IN 3

21

NC

3

+VSS

1

NC

2

IN 5

23

IN 4

22

IN 2

20

IN 1

19

ENB

18

A0

17

A1

16

A2

15

A3

14

VREF

13

IN 6

24

GND

12

IN 8

26

-VSS

27

OUT

28

IN 7

25

U52

AN MUX

+

C50

10 uF, 35V, TANTALUM

1

TP57

1

TP51

R49

100

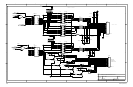

NC

1

VIN

2

TRIM

5

VOUT

6

NR

3

NC

8

GND

4

NC

7

U56

VOLTAGE REF

C43

0.15 uF, ceramic

1

TP55

C40

0.15 uF, ceramic

C49

0.15 uF, ceramic

C54

0.15 uF, ceramic

C44

.022 uF, 50V

D1

2

D2

3

D3

4

D4

5

D5

6

D6

7

D7

8

D8

9

CLK

11

OE

1

Q1

19

Q2

18

Q3

17

Q4

16

Q5

15

Q6

14

Q7

13

Q8

12

U58

74HC574

C52

0.15 uF, ceramic

C48

1.2 uF, 6.3V ceramic

1

TP53

COS

12

OPT10V

10

-VS

11

CLK

13

FOUT

14

8VI

9

10VI

8

GND

15

AGND

16

COMP-

17

COMP+

18

OP OUT

4

NC

3

+VS

2

OP-

5

OP+

6

REF

20

5VI

7

NC

19

NC

1

U54

AD652KP

D1

2

D2

3

D3

4

D4

5

D5

6

D6

7

D7

8

D8

9

CLK

11

OE

1

Q1

19

Q2

18

Q3

17

Q4

16

Q5

15

Q6

14

Q7

13

Q8

12

U60

74HC574

1

TP54

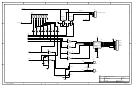

R43 100

R47100

-

+

7

2

3

4

6

U53

OP-AMP, PRECISION

1

TP49

1

2

3

4

5

6

7

8

9

10

11

12

J109

MICROFIT-12

R48 200

4

5

8

1 X1

MB100H-4.8MHZ

+

C45

10 uF, 35V, TANTALUM

R45

1M, 1%, 1206 CHIP

C46

0.15 uF, ceramic

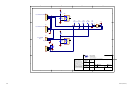

TIE

40

TIE

39

TIE

38

TIE

37

TIE

36

FREQ

35

TIE

34

TIE

12

GND

10

DB7

11

TIE

13

DB0

14

ICLK

42

TIE

33

DB3

9

RDMBYTE

8

VCCIO

32

SEL60

29

START

28

TDO

30

TDI

15

TMS

16

TCK

17

RDMSB

18

VFCLK

43

DB5

44

DB6

4

TIE

3

TIE

2

DB2

5

VCCINT

41

RDLSB

6

READ

27

SC

26

SB

25

GND

23

IOR

22

VCCINT

21

DB1

20

TIE

1

SA

24

DB4

7

TIE

19

GND

31

U57

Xilinx CPLD

C55

0.15 uF, ceramic

C

10

1

2

3

4

6

7

8

9

5

RN17

100Kx8

D1

2

S1

3

-VS

4

GND

5

S4

6

D4

7

IN4

8

IN3

9

S3

11

IN1

1

IN2

16

D2

15

S2

14

+VS

13

VCC

12

D3

10

U55

DG444DY

4

5

6

U59B

74HC32

1

2

3

U59A

74HC32

IOR

VFREAD

D[0..7]

VFPROG

DACMUX

CHGAIN

TEMPMUX

IOW

SHDN

VREF

TC6

TC7

TC8

+15V

VCC

+15V

VCC

-15V

VCC

-15V

+15V

-15V

VCC

+15V

VCC

VCC

+15V

VCC

-15V

ANALOG INPUTS

C

10

1

2

3

4

6

7

8

9

5

RN15

100Kx8

C

10

1

2

3

4

6

7

8

9

5

RN14

100Kx8

CH1

CH2

CH3

CH4

CH7

CH6

CH6

CH8

CH9

CH11

CH12

CH13

CH14

1

TP1

VREF

1

TP3

AGND

4

R9

100

PLACE 100

OHM

RESISTOR AS

CLOS AS

POSSIBLE TO

X1 AND X2

R45 induces an

offset in analog

signal to give a

'live 0' for sensors

with 0 or slightly

negative output

R47 and R48 reduce the gain

for analog inputs by 1%, so

that we can read slightly above

full scale, to prevent overflow

of ADC reading

VCC

Schematic for E Series Motherboard PCA 05702

05703 A

8

D-16

04521C (DCN5731)