123

CHAPTER 7 PROGRAMMING

7

7.3 When Using the Module in a Standard System Configuration

7.3.2 OPR program

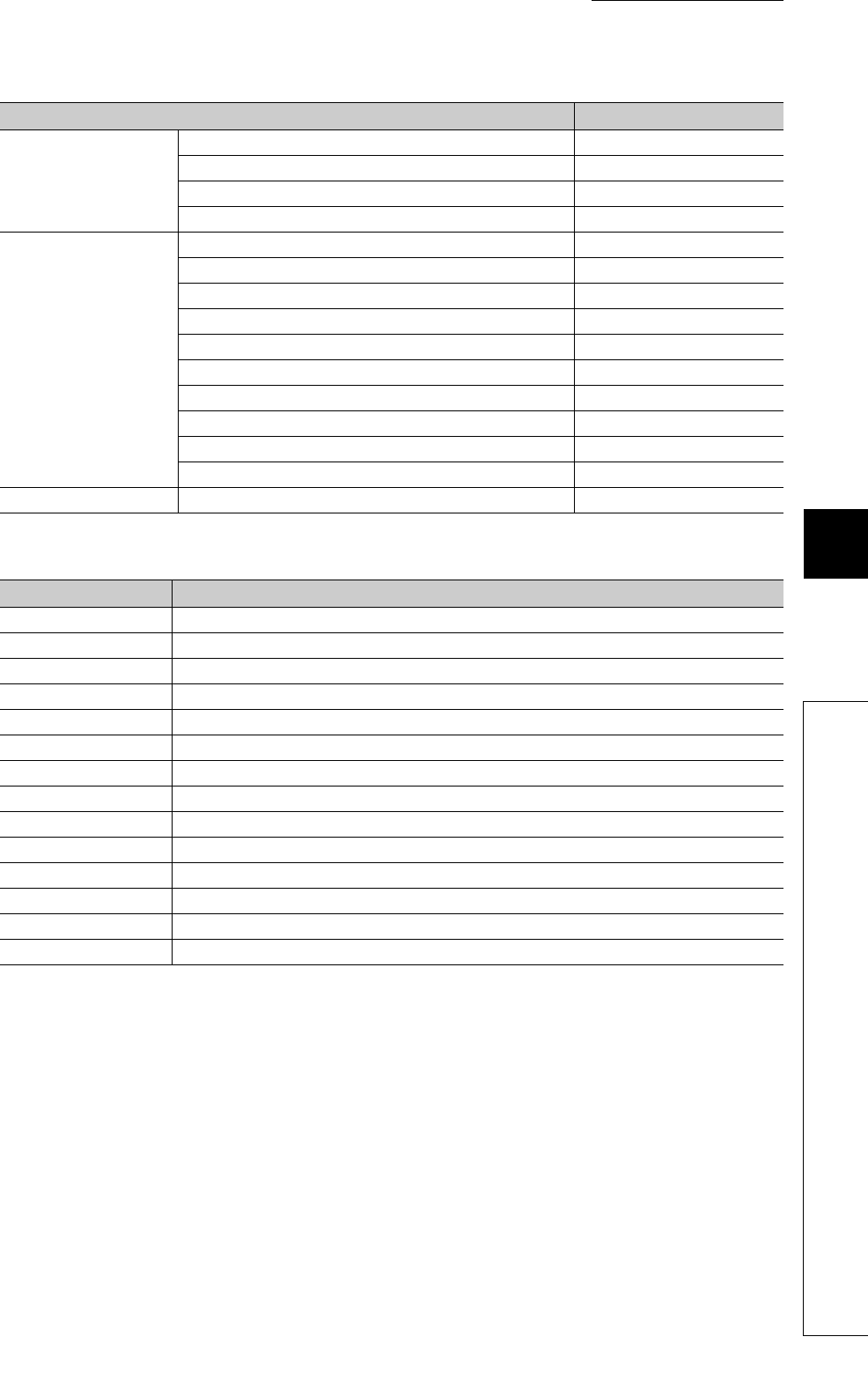

(c) Execution condition

(d) Device used by the user

Check item Condition

External I/O signal

Servo READY signal (READY) ON

Stop signal (STOP) OFF

Upper limit signal (FLS) ON

Lower limit signal (RLS) ON

I/O signal

WDT error, H/W error signal (X10) OFF

QD73A1 READY signal (X11) OFF

BUSY signal (X14) OFF

Excessive error signal (X17) OFF

Error detection signal (X18) OFF

OPR start complete signal (X20) OFF

Synchronization flag (X24) ON

OPR start signal (Y20) OFF

Stop signal (Y27) OFF

PLC READY signal (Y2D) OFF

Buffer memory OPR parameters No error

Device Description

X31 OPR command

D20 OP address (lower 16 bits)

D21 OP address (upper 16 bits)

D22 OPR speed (lower 16 bits)

D23 OPR speed (upper 16 bits)

D24 Creep speed (lower 16 bits)

D25 Creep speed (upper 16 bits)

D26 Movement amount after near-point dog ON (lower 16 bits)

D27 Movement amount after near-point dog ON (upper 16 bits)

M0 Fixed parameter setting memory

M34 OPR parameter setting memory

M35 OPR request

M37 OPR command pulse

SM402 Turns on for one scan once the CPU module is in the RUN status