19

CHAPTER 1 OVERVIEW

1

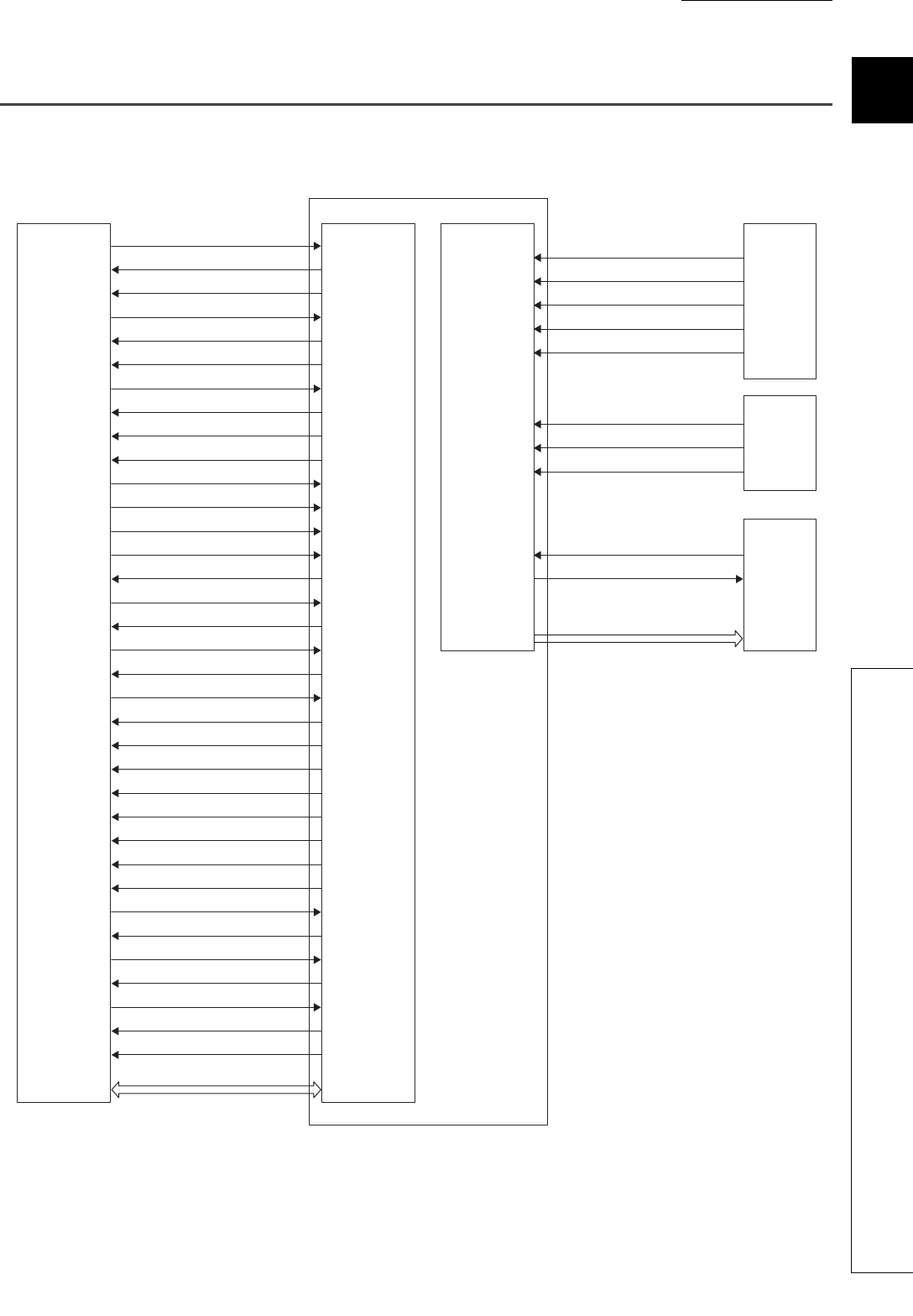

1.2 Signal Transmission Between the QD73A1 and Others

1.2 Signal Transmission Between the QD73A1 and Others

The following figure shows signal transmission between the QD73A1 and a CPU module, and a drive unit.

Y2D

X11

X12

Y20

X20

X13

Y21 to Y23

X21 to X23

X14

X15

Y2C

Y24, Y25

Y26

Y27

X18

Y28

X19

Y29

X1A

Y2A

X16

X17

X1C

X1D

X1E, X1F

X1B

X10

X24

Y1A

X2A

Y1B

X2B

Y1C

X2C

X2D

Interface with

the CPU

module

External

interface

External

control

signals

PLG

Drive unit

PLC READY signal

QD73A1 READY signal

OPR request signal

OPR start signal

OPR start complete signal

OPR complete signal

Positioning start signal

Positioning start complete signal

BUSY signal

Positioning complete signal

Speed-position switching enable signal

JOG start signal

Speed-position mode restart signal

Stop signal

Error detection signal

Error reset signal

Overflow signal

Overflow reset signal

Underflow signal

Underflow reset signal

In-position signal

Excessive error signal

Near-point dog signal

External stop signal

Upper limit signal/Lower limit signal

Servo READY signal

WDT error, H/W error signal

Synchronization flag

Zero/gain adjustment data

writing request signal

Zero/gain adjustment data

writing complete flag

Zero/gain adjustment change request signal

Zero/gain adjustment change complete flag

Set value change request signal

Set value change complete flag

Operating status of the speed-position

control switch mode

Stop signal (STOP)

Near-point dog signal (DOG)

Upper limit signal (FLS)

Lower limit signal (RLS)

Speed-position switching command signal

(CHANGE)

Phase-Z pulse (Zero signal)

Phase-A pulse

Phase-B pulse

Servo READY signal (READY)

Servo ON signal (SVON)

CPU module

QD73A1

Analog voltage

Data writing/reading